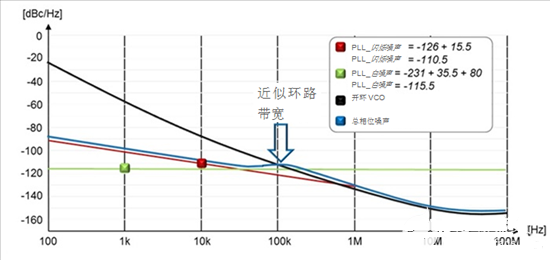

- 也许你也会跟我一样认为典型数据表中的某些规格难以理解,这是因为其中涵盖了一些你不太熟悉的隐含惯例。对许多RF系统工程师而言,其中一种规格便是锁相环(PLL)中的相位噪声。当信号源被用作本机振荡器(LO)或高速时钟时,相位噪声性能对满足系统要求起到了重要作用。最初从数据表中推断出该规格时似乎就像一个独立的项目。下面我来讲解一下如何通过读取PLL的相位噪声规格来对您的无线电或高速应用可达到的性能进行初步评估。 注意,PLL是一种控制回路,这种系统具备频率响应功能。参考路径中生成的噪声受控于回路中对系统输

- 关键字:

PLL VCO

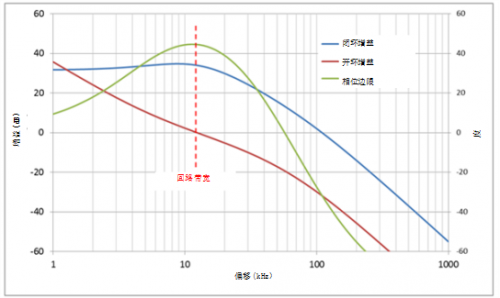

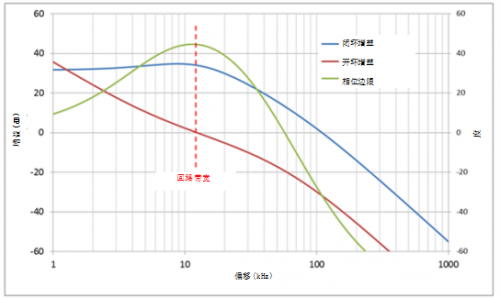

- 假设您已经通过迭代信息传递相位边限和回路带宽在锁相环(PLL)上花费了一些时间。但遗憾地是,还是无法在相位噪声、杂散和锁定时间之间达成良好的平衡。感到泄气?想要放弃?等一下!你是否试过伽马优化参数? 伽马优化参数 伽马是一个数值大于零的变量。当伽马等于1时,相位边限在回路频处会达到最大值(图1)。很多回路滤波器设计方法把伽马值设为1,这是个很好的起点,但还有进一步优化的空间。 图1:伽马等于1时的波德图 伽马能够有效用于优化带内相位噪声,尤其是因压控振荡器 (VCO) 带来

- 关键字:

PLL 回路滤波器

- 假设您已经通过迭代信息传递相位边限和回路带宽在锁相环(PLL)上花费了一些时间。但遗憾地是,还是无法在相位噪声、杂散和锁定时间之间达成良好的平衡。感到泄气?想要放弃?等一下!你是否试过伽马优化参数? 伽马优化参数 伽马是一个数值大于零的变量。当伽马等于1时,相位边限在回路频处会达到最大值(图1)。很多回路滤波器设计方法把伽马值设为1,这是个很好的起点,但还有进一步优化的空间。 图1:伽马等于1时的波德图 伽马能够有效用于优化带内相位噪声,尤其是因压控振荡器 (VCO) 带来

- 关键字:

PLL 滤波器

- 模拟锁相环电路锁定检测问题解答 1.PLL锁定有那些检测方法,它们特点是什么? 一种是最为简单的数字检测,它利用输入参考的分频信号与VCO反馈的分频信号,在PFD里鉴相的结果,通过连续结果时钟周期检测到鉴相的脉宽小于某值,作为锁定的有效判决规则。这种检测方式,判决方式简单,判断的结果只有锁定和非锁定两种情况。 另一种方式是模拟锁定检测,也称为N沟道漏级开路检测,它的实现原则是通过对于PFD输出的超前和滞后脉冲做XOR操作,直接将得出的结果输出。由于XOR的结果有是一串高低的脉冲,所以需要外部电路

- 关键字:

锁相环 PLL

- 经常有要阻挡某些频率信号的情况,其中最常见的是50Hz或60Hz的电力线工频。图1中的PLL陷波滤波器可以用于阻拦不需要的频率。IC1LM567C是一只音调解码器。C1、R1A和R1B等元件决定了IC1探测的频率F:F=1/[C1(R1A+R1B)]。...

- 关键字:

PLL 陷波滤波器

- 随着数据转换器的速度和分辨率不断提升,对具有更低相位噪声的更高频率采样时钟源的需求也在不断增长。时钟输入面临的积分相位噪声(抖动)是设计师在设计蜂窝基站、军用雷达系统和要求高速和高性能时钟信号的其他设计

- 关键字:

PLL 双环路 相位噪声

- 时钟速度的提高和更严格的信号时序增加了对精准的高频模块的需求。PLL(锁相环)基于输入信号生成高频输出信号,是一种备受欢迎的用于产生高频信号的电路。当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称

- 关键字:

PLL 时间测量

- 宽带通信系统通常需要超低噪声调节器来为VCO和PLL供电。调节器还必须能够抑制其输入端出现的任何纹波。在一般系统中,交流输入转换为隔离式直流供电轨,例如-48 V直流。该供电轨继而转换为隔离式12 V系统轨,为通信

- 关键字:

超低噪声调节器 PLL VCO 时钟IC 供电轨

- 我们可能都见到过需要随时间变化扫描频率的情况。如果您遇到这样的问题,可以考虑雷达等应用,在这类应用中发送的信号不仅可由目标反射回来,而且还能够与接收到的信号进行比较,如下图 1 所示。观察频率 (Df) 差异

- 关键字:

PLL 调制波形 波形调制

- 十几年前,频率控制行业推出了基于锁相环(PLL)的振荡器,这是一项开拓性创新技术,采用了传统晶体振荡器(XO)所没有的多项特性。凭借内部时钟合成器IC技术,基于PLL的XO可编程来支持更宽广的频率范围。这一突破消除了

- 关键字:

锁相环 PLL 振荡器 抖动 相位噪声

- 对锁相环环路滤波器进行简单分析,对ADIsimPLL 3.1模拟软件的功能特点做了简要介绍,并利用仿真软件对一款频率合成器的环路滤波器进行仿真设计,结果表明该软件在设计应用中方便快捷,能够帮助设计出满足指标要求且性能稳定的环路滤波器。

- 关键字:

环路带宽 PLL 环路滤波器 压控灵敏度

- 在尝试将锁相环(PLL)锁定时,你是否碰到过麻烦?草率的判断会延长调试过程,调试过程变得更加单调乏味。根据以下验证通行与建立锁定的程序,调试过程可以变得非常简单。

第1步:验证通信

第一步是验证PLL响应编程的能力。如果PLL没有锁定,无法读回,则尝试发送需要最小量硬件命令工作的软件命令。一种方法是通过软件(而非引脚)调节PLL的通电断电寻找引脚的可预测电流变化或偏置电压电平变化。许多PLL在其输入(OSCin)引脚的电平在通电时为Vcc/2,在断电时为0V。

如果PLL集成了压控振

- 关键字:

锁相环 PLL

- 美普思科技公司(MIPS Technologies, Inc., 纳斯达克代码:MIPS)宣布,新推出的SkypeKit™开发工具可提供MIPSTM架构对Skype的支持。通过SkypeKit 封闭测试(beta)计

- 关键字:

MIPS-Based Skype MIPS

pll-based介绍

您好,目前还没有人创建词条pll-based!

欢迎您创建该词条,阐述对pll-based的理解,并与今后在此搜索pll-based的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473