根据低码率实时应用领域的特点,设计了一种H.264视频编码系统。采用FPGA的NiosII CPU架构,自定义硬件模块实现H.264.实时压缩编码。实验验证表明,H.264编码器对CIF大小的图像实现了实时编码,能满足对低码率实时应用的编码要求。

关键字:

编解码器 H.264 NiosII CPU

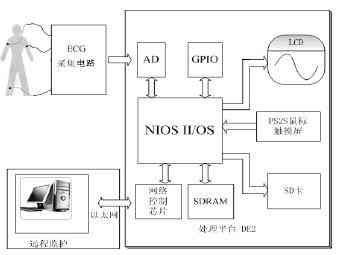

HHCE(Home Health Care Engineering)这门学科正随着人类对健康的重视和远程医疗的发展而逐渐走进人们的生活。它提倡的是一种“在家就医,自我保健,远程诊断”的理念,把高科技与医疗结合起来。HHCE的出现符合21世纪社会老龄化、医疗费用日益高涨以及人们生活健康质量高要求的趋势,同时可实现医疗资源共享,提高边远地区的医疗水平,因此具有特别旺盛的生命力。HHCE系统提供一种对于家庭、社区医疗、出诊医生有效便捷的医疗监测解决方案,具有心电信号监测功能的监测器是

关键字:

SOC SOPC FPGA 便携式 NiosII

引言

随着电子技术的发展,人们不断地追求更好的新型存储设备。目前海量存储领域中的主流产品非硬盘莫属,而固态盘则被认为是一种最有可能取代硬盘的全新解决方案。与硬盘相比,其主要的优势在于能够达到更高速度、更小体积、更低功耗、更小噪声、更高可靠性,同时与硬盘一样使用方便。

广义上讲,固态盘设备包括所有使用半导体芯片作为存储介质的存储设备,例如使用动态RAM存储数据的某些特定设备,或是CF/SD/MMC卡等同样使用闪存存储数据但使用了其他接口的存储设备;但狭义上讲,固态盘仅指使用NAND型闪存存储

关键字:

NiosII 固态盘 硬盘 闪存 ATA

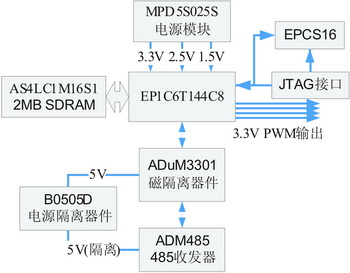

针对于列车控制系统半实物仿真平台测速测距模块的多通道PWM信号测量/产生的要求,提出了一种利用NiosII软核处理器替代通讯用MCU的智能多通道PWM信号测量/产生器的设计方案。

关键字:

NiosII PWM FPGA SOPC 200807

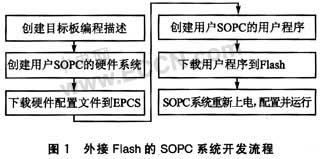

1 Flash在SOPC中的作用

Flash在SOPC中的作用主要表现在两方面:一方面,可用Flash来保存FPGA的配置文件,从而可以省去EPCS芯片或解决EPCS芯片容量不够的问题。当系统上电后,从Flash中读取配置文件,对FPGA进行配置。另一方面,可用Flash来保存用户程序。对于较为复杂的SOPC系统,用户程序一般较大,用EPCS来存储是不现实的。系统完成配置后,将Flash中的用户程序转移到外接RAM或片内配置生成的RAM中,然后系统开始运行。

2 Flash编程的实现

关键字:

FPGA SOPC Flash RAM NiosII

引 言

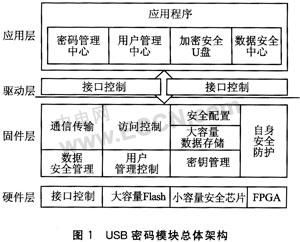

密码模块是指被容纳在加密边界范围中,执行认可安全功能(包括加密算法与密钥产生)的硬件、软件和固件的组合。集加密存储、安全认证等功能于一体的USB密码模块,可作为USB安全钥载体、USB加密卡、USB大容量加密存储体应用于保护信息系统和秘密信息的主要工具,具有十分良好的市场应用背景。

SOPC(System On a Programmable Chip)技术是一种灵活、高效的软硬件综合解决方案。硬件上可裁剪、可扩充、可升级,有丰富的IP核可供集成,使得设计变得十分灵活。

本文提

关键字:

SOPC USB 密码模块 嵌入式 控制器 NiosII MCU 固件

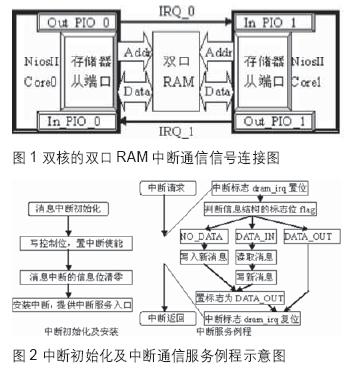

本文研究了NiosII多核处理器之间几种不同的通信方案机制和方法,并完成了测试验证。最后对几种方案作出总结比较,提出其适用范围。文中提出的邮箱内核和共享存储的多核通信方案在笔者的PDA考评系统项目中得到了应用。

关键字:

NiosII 多核处理器 多核通信

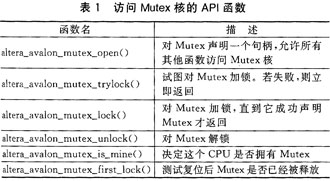

摘要 详细地阐述基于NiosIl和FPGA的多处理器系统的实现机制,讨论利用硬件互斥核实现多处理器资源共享的方法,并给出硬件设计的具体步骤以及软件设计、调试方法和关键技术;利用Altera公司提供的QuartusII、SOPC Builder和NiosII IDE等开发工具,通过一个3处理器系统设计实例,验证了设计方法的正确性,实现了3处理器对存储器资源的共享。

关键词 SOPC NiosII 多处理器系统 共享存储器

两个或多个微处理器一起工作来完成某个任务的系统称为“多处理

关键字:

SOPC NiosII 多处理器系统 共享存储器

NiosII嵌入式系统的一个重要问题就是软件代码量的大小,这关系到存放代码的存储器件容量大小,因此控制和减小程序代码量是降低系统成本的重要方法,必须首先从处理器的启动顺序开始研究。

关键字:

NiosII 处理器 软件代码 方法

摘 要:介绍了如何在基于NiosII的SOPC中设计EEPROM的Controller Core,用Verilog HDL实现其硬件部分,编写了相关驱动程序和应用层软件,构建了基于NiosII的SOPC。并以AT24C02为例,在Altera的Stratix1S10的FPGA上实现了通过EEPROM Controller对其进行读写,试验结果正确。关键词:NiosII; SOPC; EEPROM Controller&nbs

关键字:

嵌入式系统 单片机 NiosII SOPC EEPROM Controller 嵌入式

本文简要介绍了Nios II设计架构,然后通过一个USB控制器的接口模块设计实例,详细介绍了Nios II设计中用户自定义逻辑的实现方法和效果,同时给出了对USB控制器SL811HS的底层读写函数。

关键字:

NiosII USB 接口 模块设计

瑞萨科技公司宣布,推出符合HDMI*1V1.3高速数字接口标准的R8J66030FT HDMI接收器,该器件适用于平板电视。样品交付将于2007年4月在日本开始。 R8J66030FT是一种高性能的HDMI接收器,也是业界第一个提供符合HDMI™V1.3标准的输入端口和CEC*2控制功能的单芯片器件。使用这个接收器有助于改善具备HDMI的LCD、等离子等平板电视的功能并降低成本。 <产品背景> HDMI是一个用于数字视听产品的数字接口,有助于通过一条电缆实

关键字:

HDMI Renesas V1.3 高速数字接口标准 接收器 平板电视 通讯 网络 无线 消费电子 消费电子

通过PCI EXPRESS兼容性测试 - 赛灵思VIRTEX-5 成为全球首个通过所有v1.1标准测试的FPGA 经验证的解决方案使用户可快速采用业界速度最快的、内建低功耗PCI Express 端点模块和串行收发器的65nm FPGA 灵思公司( Xilinx, Inc. (NASDAQ: XLNX))宣布其Virtex™-5&nbs

关键字:

FPGA v1.1标准测试 单片机 嵌入式系统 赛灵思VIRTEX-5

通过PCI EXPRESS兼容性测试 - 赛灵思VIRTEX-5 成为全球首个通过所有v1.1标准测试的FPGA 经验证的解决方案使用户可快速采用业界速度最快的、内建低功耗PCI Express 端点模块和串行收发器的65nm FPGA 赛灵思公司宣布其Virtex™-5 LXT FPGA通过了最新的PCI Express端点 v1.1

关键字:

FPGA v1.1标准 VIRTEX-5 测试 单片机 嵌入式系统 赛灵思 测试测量

lj-fn300-niosii-start-v1介绍

您好,目前还没有人创建词条lj-fn300-niosii-start-v1!

欢迎您创建该词条,阐述对lj-fn300-niosii-start-v1的理解,并与今后在此搜索lj-fn300-niosii-start-v1的朋友们分享。

创建词条

lj-fn300-niosii-start-v1电路

lj-fn300-niosii-start-v1相关帖子

lj-fn300-niosii-start-v1资料下载

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473