- 对于利用LabVIEW FPGA实现RIO目标平台上的定制硬件的工程师与开发人员,他们可以很容易地利用所推荐的组件设计构建适合其应用的、可复用且可扩展的代码模块。基于已经验证的设计进行代码模块开发,将使现有IP在未来应

- 关键字:

LabVIEW FPGA IP核 模块设计

- 全球电子设计创新领先企业Cadence设计系统公司 (NASDAQ: CDNS),日前宣布Nufront(新岸线)的NS115芯片组采用了Cadence可配置的DDR3/3L/LPDDR2存储控制器与硬化PHY IP核,应用于其双核ARM Cortex –A9移动应用处理器。TSMC 40LP工艺, 32位DDR3/LPDDR2接口的数据传输速率最高可达800Mbps,并能提供对超薄笔记本、平板电脑和智能手机等产品至关重要的基于数据流量的自动功耗管理。 Cadence 的DDR3/3L/LPDDR2 IP

- 关键字:

Cadence DDR2 IP核

- Leon2是GaislerResearch公司于2003年研制完成的一款32位、符合IEEE-1754(SPARCVS)结构的处理器IP核。它的前 ...

- 关键字:

Leon2 处理器 IP核

- Cosmic Circuits,领先的差异化模拟和混合信号IP核提供商,宣布开发MIPI D-PHY、MIPI M-PHY、USB2.0、USB3.0、PCI Express和HDMI IPs标准的28纳米和20纳米IP核。Cosmic Circuits也正在开发这些标准的控制器解决方案,以便为客户提供完整的解决方案。

Cosmic Circuits提供差异化混合信号IP核的广泛组合,提供的产品大致分为两类:AMS(模拟和混合信号)IP核和连接(接口)IP核。Cosmic Circuits的AM

- 关键字:

半导体 IP核

- 引言随着半导体技术的发展,深亚微米工艺加工技术允许开发上百万门级的单芯片,已能够将系统级设计集成...

- 关键字:

SoC设 IP核 接口技术

- 引言随着半导体技术的发展,深亚微米工艺加工技术允许开发上百万门级的单芯片,已能够将系统级设计...

- 关键字:

IP核 SoC 接口技术

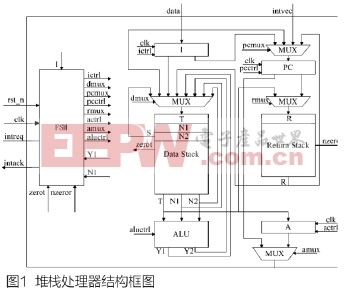

- 堆栈处理器是一种专门面向嵌入式控制领域的处理器,其所有执行过程均依赖于两个硬件支持的堆栈:执行数学表达式的数据堆栈(Data Stack)和保存子程序返回地址的返回堆栈(Return Stack),而不是大量的通用寄存器。堆栈处理器的特征使其相比较于RISC和CISC等通用寄存器处理器,更加适合应用于嵌入式实时控制领域。本文在上述背景下,介绍了一个堆栈处理器的IP核,给出了其在Digilent公司的Nexys 3开发板上的实现结果,以及使用ModelSim SE 6.5C仿真测试的结果。

- 关键字:

嵌入式 IP核

- 随着PC机和外围设备的发展,传统的并行接口和串行接口RS-232在易用性(即插即用)和端口扩展等方面存在着一定...

- 关键字:

USB2.0接口 IP核 传输速率

- 1 引言 长期以来,单片机以其性价比高、体积小、功能灵活等方面的独特优点被广泛应用。但受其内部资 ...

- 关键字:

51单片机 IP核

- 1 引言 随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合为一个系统,提高了设计效率,加快了设计过程,缩短了产品上市时间。但是随着设

- 关键字:

BIST IP核 测试方案

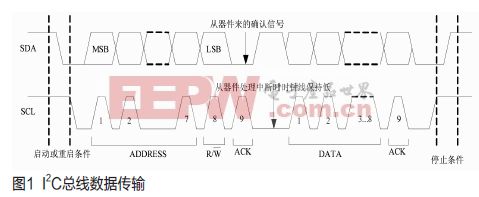

- I2C总线作为一种事实上的国际标准,在超过100种不同的IC上实现并且得到超过50家公司的许可。它具有连线少,结构简单的特点。本文介绍了一种高速I2C从器件接口电路IP核设计。在系统应用中,单片机作为主控器件,本IP核作为从器件中的接口电路,它们通过I2C总线相连,实现MCU对IC或FPGA中相关寄存器的访问。从而代替了MCU通用的地址数据接口,大大减少了IC或FPGA的管脚数量,节省了I/O资源,这对于I/O资源紧张的IC设计和FPGA开发是非常有意义的。

- 关键字:

FPGA I2C总线 IP核 201107

- 摘要:针对目前在嵌入式平台中使用SD卡控制器专用芯片价格昂贵、软件模拟SPI时序控制读写速度较慢的问题...

- 关键字:

控制器 IP核 Quartus II

- 近年来,随着现场可编程门阵列(FPGA)在雷达信号处理中的广泛应用以及FPGA芯片技术的发展,为大家提供了一种较好...

- 关键字:

调频信号 IP核 脉冲压缩

ip核介绍

IP核概述

IP核则是一段具有特定电路功能的硬件描述语言程序,该程序与集成电路工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片。利用IP核设计电子系统,引用方便,修改基本元件的功能容易。具有复杂功能和商业价值的IP核一般具有知识产权,尽管IP核的市场活动还不规范,但是仍有许多集成电路设计公司从事IP核的设计、开发和营销工作。IP核有两种,与工艺无关的VHDL程序称为软核;具有特定电路 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473