软件开发早在 2003 年,该软件就启动了。这是在设计周期开始时获取的第一批屏幕截图之一。图形用户界面GUI 变化很快。这是更高版本。触发器像所有普通示波器一样,有 3 种触发器:单次:显示一次跟踪(发生触发时)。与“手臂”按钮配合使用。正常:每次触发发生时显示跟踪,如果触发器未发生,则不显示任何内容。自动:触发时显示跟踪,如果半秒内没有触发,则仍然显示跟踪。坚持添加了持久性功能,可以一次记住和显示多达 16 帧(它会淡化旧帧)。周期重建(“样本等效时间”技术)一个有趣的功能是能够显示一个周期(周期信号)

关键字:

FPGA 数字示波器

Flashy是一款高速模拟采集板。它通常与FPGA板一起使用,以创建数字示波器。这是一个单通道 Flashy(顶板),带有 BNC 连接器和 Pluto-II(底板)。 该组合构成了单通道 100MSPS(每秒兆采样数)数字示波器。Flashy 板有三种速度等级:具有ADC60的08060MHz振荡器(典型工作频率范围为20MHz至70MHz)具有ADC100的08100MHz振荡器(典型工作频率范围为20MHz至125MHz)125MHz/133MHz振荡器,带ADC08200(典型工作频率范

关键字:

FPGA 数字示波器 Flashy 采集板

现在示波器骨架已开始工作,可以轻松添加更多功能。边沿斜率触发让我们添加在上升沿或下降沿触发的能力。 任何示波器都可以做到这一点。我们需要一点信息来决定我们想要触发的方向。 让我们使用 PC 发送的数据的 bit-0。assign Trigger = (RxD_data[0] ^ Threshold1) & (RxD_data[0] ^ ~Threshold2);这很容易。更多选项让我们添加控制触发阈值的功能。 这是一个 8 位值。 然后我们需要水平采集速率控制、滤波控制...... 这需

关键字:

FPGA 数字示波器

我们的第一个触发因素很简单 - 我们检测到上升沿越过固定阈值。 由于我们使用的是 8 位 ADC,因此采集范围从 0x00 到 0xFF。因此,让我们暂时将阈值设置为0x80。检测上升沿如果样本高于阈值,但前一个样本低于阈值,则触发!reg Threshold1, Threshold2;always @(posedge clk_flash) Threshold1 <= (data_flash_reg>=8'h80);always @(posedg

关键字:

FPGA 数字示波器

FIFO使我们能够非常快速地获得工作设计。但对于我们简单的示波器来说,这有点矫枉过正。我们需要一种机制来存储来自一个时钟域(100MHz)的数据,并在另一个时钟域(25MHz)中读取数据。 一个简单的双端口RAM就可以做到这一点。 缺点是两个时钟域之间的所有同步(FIFO为我们所做的)现在必须“手动”完成。触发“基于 FIFO”的示波器设计没有明确的触发机制。让我们改变一下。 现在,每次从串行端口接收到字符时,示波器都会被触发。 当然,这仍然不是一个非常有用的设计,但我们稍后会对其进行改进。我们使用“as

关键字:

FPGA 数字示波器

以下是此处构建的内容:FPGA 接收两个时钟:一个缓慢的“系统”时钟,固定在25MHz。ADC采样时钟(更快,假设100MHz),连接到ADC和FPGA。拥有这两个时钟为设计提供了灵活性。 但这也意味着我们需要一种方法将信息从一个时钟域传输到另一个时钟域。 为了验证硬件是否正常工作,让我们走一条简单的路线,使用FIFO。 从ADC采集的样本以全ADC速度(100MHz)存储在FPGA FIFO中。然后,FIFO内容被读回、序列化,并以更慢的速度(115200波特)在串行端口上发送。 最后,我们将串行输出连

关键字:

FPGA 数字示波器

与模拟示波器相比,数字示波器具有许多优势,例如能够捕获单个事件,并显示触发前发生的情况。您只需将ADC和FPGA连接在一起,即可构建数字示波器。这种特殊设计使用100MHz闪存ADC,因此我们正在构建一个100MSPS(每秒兆采样数)示波器。这种示波器设计很有意思,因为它展示了现代 FPGA 的强大和实用性。 但是,如果您不熟悉 FPGA 技术,请记住,这不是本网站上最容易理解的设计。HDL设计或者如何在FPGA内部创建示波器逻辑。HDL 第 1 部分 - 基于 FIFO 的设计。HDL 第 2

关键字:

FPGA 数字示波器

尽管现代 FPGA 包含内部存储器,但可用存储器量始终比专用存储芯片低几个数量级。 因此,许多FPGA设计人员将某种类型的存储器附加到他们的FPGA中也就不足为奇了。 特别是,SDRAM因其高速和低成本而成为非常受欢迎的存储器。 不幸的是,它们不像静态存储器那样容易控制,因此经常使用SDRAM控制器。对于我们的控制器,我们的目标是可能是最简单的SDRAM:美光MT48LC1M16A1 16Mb传统SDRAM。 我们的测试系统包括 Xylo-E、Xylo-EM 和 Xylo-LM(具有 16Mb

关键字:

FPGA SDRAM控制器

HDMI 是一种数字视频接口,因此很容易从现代 FPGA 驱动。让我们看看它是如何工作的。连接器标准 HDMI 连接器有 19 个引脚。 在 19 个引脚中,有 8 个特别值得关注,因为它们形成 4 个 TMDS 差分对来传输实际的高速视频信息。TMDS 时钟+ 和时钟-TMDS data0+ 和 data0-TMDS data1+ 和 data1-TMDS data2+ 和 data2-我们从FPGA到HDMI连接器的连接再简单不过了......我们使用 8 个 FPGA 引脚,配置为 4 个差分 TM

关键字:

FPGA HDMI接口

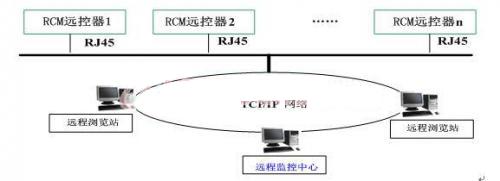

以太网全双工协议易于在FPGA中实现。 这里的目标是将FPGA连接到10BASE-T连接。以太网数据包:发送和接收10BASE-T FPGA 接口 0 - 发送以太网流量的方案在这里,我们演示了如何将以太网流量直接从FPGA发送到PC。对于此食谱,您需要:FPGA 开发板,具有 2 个空闲 IO 和一个 20MHz 时钟。一台带有以太网卡并安装了 TCP-IP 堆栈的 PC(如果你能浏览 Internet,你就很好)。(可选)网络集线器或交换机。1. 将FPGA板连接到以太网以下是使用以太网集线器或交换机

关键字:

FPGA Ethernet接口

随着 PCI Express 在高端 FPGA 中变得司空见惯,让我们看看 FPGA 供应商如何轻松实现该技术。特别是,我们更仔细地研究了赛灵思的 PCI Express 解决方案。PCI Express 1 - 连接器PCI Express 通常有两种尺寸:1 通道和 16 通道,其中 1 通道用于普通主板,16 通道用于显卡。连接器1 通道连接器有 36 个触点,排列成两排,每排 18 个触点。这是俯视图。在 36 个触点中,只有 6 个对数据传输有用,其余是电源引脚和其他辅助信号。 6 个功能触点以

关键字:

FPGA PCI Express接口 赛灵思

FPGA 是功能强大的 PCI 开发平PCI 0 - 简单的PCI接口这是 PCI 代码的一个示例。 我们使用 PCI 写入命令来控制 LED。 写“0”可关闭 LED,写“1”可打开 LED!台,这要归功于其可重新编程性和运行速度。// Very simple PCI target// Just 3 flip-flops for the PCI logic, plus one to hold the state of an LEDmodule PCI(CLK, RSTn, FRAMEn, AD, CBE

关键字:

FPGA PCI接口

SD 卡可轻松与 FPGA 连接。我们的SD卡项目分为两部分:SD 卡 1 - FPGA 连接SD 卡可轻松与 FPGA 连接。 它们有不同的尺寸(标准、迷你和微型),但在电气上它们的工作方式相同。 让我们关注 micro-SD 卡,因为它们非常小且现在很受欢迎。Micro-SD 卡有 8 个针脚。首先,电源连接在引脚 4 和 6 上。然后,您需要 3 到 6 个 FPGA 引脚连接,具体取决于您决定使用的操作模式。SPI模式在SPI模式下,DI/DO线是单向的。这意味着:无需在 DI/DO 上上拉命令(

关键字:

FPGA SD卡

大多数FPGA都支持JTAG。JTAG 1 - 什么是JTAG?JTAG 是 1149 年代开发的 IEEE 标准 (1.1980),用于解决电子板制造问题。 如今,它更多地用作编程、调试和探测端口。但首先,让我们看看JTAG的原始用途,边界测试。边界测试这是一个简单的电子板(也称为“PCB”,意为“印刷电路板”),带有两个 IC(“集成电路”)、一个 CPU 和一个 FPGA。典型的电路板可能有更多的IC。IC可以有很多引脚。 因此,当然,IC通过许多连接(PCB走线)连接在一起。我们在这里只展示四个。

关键字:

FPGA JTAG接口

时序约束的概念和基本策略时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。例如用OFFSET_IN_BEFORE约束可以告诉综合布线工具输入信号在时钟之前什么时候准备好,综合布线工具就可以根据这个约束调整与IPAD相连的Logic Circuitry的综合实现过程,使结果满足FFS的建立时间要求。附加时序约束的一般策略是先附加

关键字:

FPGA 约束 时序

fpga:quartusⅡ介绍

您好,目前还没有人创建词条fpga:quartusⅡ!

欢迎您创建该词条,阐述对fpga:quartusⅡ的理解,并与今后在此搜索fpga:quartusⅡ的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473