实验任务任务:基于 STEP-MAX10M08核心板 和 STEP BaseBoard V3.0底板 完成简易电子琴设计并观察调试结果要求:按动矩阵键盘,驱动底板无源蜂鸣器发出产生不同音调,弹奏一首《小星星》。解析:通过FPGA编程驱动矩阵键盘电路,获取矩阵键盘键入的信息,然后通过编码将键盘输出的信息译码成对应的音节数据,最后通过PWM发生模块驱动底板上的无源蜂鸣器发出声音。实验目的在基础数字电路实验部分我们已经掌握了FPGA设计PWM信号发生器的原理及方法,上节实验中又学习了矩阵键盘的驱动原理及方法,本

关键字:

FPGA 电子琴 STEP-MAX10M08 STEP BaseBoard V3.0

简易交通灯:本节将向您介绍Verilog语法之中的精髓内容——状态机,并且将利用状态机实现十字路口的交通灯。====硬件说明与实现项目框图====上图为十字路口交通示意图分之路与主路,要求如下:交通灯主路上绿灯持续15s的时间,黄灯3s的时间,红灯10s的时间;交通灯支路上绿灯持续7s的时间, 黄灯持续3秒的时间,红灯18秒的时间;根据上述要求,状态机设计框架分析如下:S1:主路绿灯点亮,支路红灯点亮,持续15s的时间;S2:主路黄灯点亮,支路红灯点亮,持续3s的时间;S3:主路红灯点亮,支路绿灯点亮,持

关键字:

交通灯 状态机 FPGA Lattice Diamond 小脚丫

简易交通灯:本节将向您介绍Verilog语法之中的精髓内容——状态机,并且将利用状态机实现十字路口的交通灯。硬件说明与实现项目框图上图为十字路口交通示意图分之路与主路,要求如下: * 交通灯主路上绿灯持续15s的时间,黄灯3s的时间,红灯10s的时间; * 交通灯支路上绿灯持续7s的时间, 黄灯持续3秒的时间,红灯18秒的时间;根据上述要求,状态机设计框架分析如下: * S1:主路绿灯点亮,支路红灯点亮,持续15s的时间; * S2:主路黄灯点亮,支路红灯点亮,持续3s的时间; * S3:主路红灯点亮,支

关键字:

交通灯 状态机 FPGA Lattice Diamond 小脚丫

呼吸灯:本节,我们将通过脉宽调制技术来实现“呼吸灯”,实现LED的亮度由最暗逐渐增加到最亮,再逐渐变暗的过程。 脉冲宽度调制(PWM:Pulse Width Modulation),简称脉宽调制。它是利用微控制器的数字输出调制实现,是对模拟电路进行控制的一种非常有效的技术,广泛应用于测量、通信、功率控制与变换等众多领域。硬件说明呼吸灯的设计较为简单,我们使用12MHz的系统时钟作为高频信号做分频处理,调整占空比实现PWM,通过LED灯LD1指示输出状态。实现原理如上图所示,脉冲信号的周期为T,高电平脉冲宽

关键字:

呼吸灯 FPGA Lattice Diamond 小脚丫

1 小型和中端FPGA服务嵌入式AI领域 莱迪思经过40多年的发展,目前拥有公司历史上最强大的产品组合,其针对AI优化、低功耗FPGA解决方案主要面向小型和中端FPGA市场。莱迪思旨在满足客户对各种网络边缘应用日益增长的智能需求,提供超强适应性的解决方案,帮助客户跟进不断发展的AI算法。莱迪思提供包括嵌入式AI在内的领先的解决方案,服务于工业、汽车、通信、计算和消费类应用。莱迪思sensAI™解决方案集合帮助客户实现最新的工厂自动化和工业机器视觉应用,其低功耗FPGA提供

关键字:

202311 FPGA 莱迪思

近日,以“创新加速,塑造FPGA芯未来”为主题的2023年英特尔® FPGA中国技术日在北京成功举行。期间,英特尔不仅披露了包括Agilex® 3系列、Agilex® 5系列在内的多款FPGA产品细节及其早期验证计划,同时亦分享了与产业伙伴在数据中心、AI、网络、嵌入式等关键领域的诸多应用,旨在以逐步扩大的产品组合进一步满足广泛细分市场需求的同时,深度展示英特尔在加速可编程创新、推动中国行业数智化进程上的重要作用。英特尔可编程方案事业部中国总经理叶唯琛表示,“在新场景、新应用海量增长的驱动下,中国本地市场

关键字:

英特尔 FPGA

计时控制在之前的实验中我们掌握了如何进行时钟分频、如何进行数码管显示与按键消抖的处理,那么在本节实验之中,我们将会实现一个篮球赛场上常见的24秒计时器。====硬件说明====在之前的实验中我们为读者详细介绍过小脚丫MXO2板卡上的按键、数码管、LED等硬件外设,在此不再赘述。本节将实现由数码管作为显示模块,按键作为控制信号的输入(包含复位信号和暂停信号),Altera MAX10作为控制核心的篮球读秒系统,实现框图如下:====Verilog代码====// *****************

关键字:

计时器 FPGA Lattice Diamond 小脚丫

Warning: file_get_contents(https://www.eetree.cn/wiki/_media/%E8%AE%A1%E6%97%B6%E5%99%A8%E6%A1%86%E5%9B%BE.png?w=800&tok=0acdce): failed to open stream: HTTP request failed! HTTP/1.1 403 Forbidden

in /var/www/html/www.edw.com.cn/www/rootapp/controll

关键字:

计时器 FPGA Lattice Diamond 小脚丫

按键消抖在之前的实验中我们学习了如何用按键作为FPGA的输入控制,在本实验中将学习如何进行按键消抖,用按键完成更多的功能。====硬件说明====按键是一种常用的电子开关,电子设计中不可缺少的输入设备。当按下时使开关导通,松开时则开关断开,内部结构是靠金属弹片来实现通断。按键抖动的原理抖动的产生 :通常的按键所用的开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,为了不产生这种现

关键字:

消抖 FPGA Lattice Diamond 小脚丫

按键消抖在之前的实验中我们学习了如何用按键作为FPGA的输入控制,在本实验中将学习如何进行按键消抖,用按键完成更多的功能。硬件说明按键是一种常用的电子开关,电子设计中不可缺少的输入设备。当按下时使开关导通,松开时则开关断开,内部结构是靠金属弹片来实现通断。按键抖动的原理抖动的产生 :通常的按键所用的开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,为了不产生这种现象而作的措施就是

关键字:

消抖 FPGA Lattice Diamond 小脚丫

在时钟分频实验中我们练习了如何处理时钟,接下来我们要学习如何利用时钟来完成时序逻辑。====硬件说明====流水灯实现是很常见的一个实验,虽然逻辑比较简单,但是里面也包含了实现时序逻辑的基本思想。要用FPGA实现流水灯有很多种方法,在这里我们会用两种不同的方法实现。1,模块化设计:在之前的实验中我们做了3-8译码器和时钟分频,如果把这两个结合起来,我们就能搭建一个自动操作的流水LED显示。框图如下:2,循环赋值:这是一种很简洁的实现流水灯效果逻辑,就是定义一个8位的变量,在每个时钟上升沿将最低位赋值给最高

关键字:

流水灯 FPGA Lattice Diamond 小脚丫

在时钟分频实验中我们练习了如何处理时钟,接下来我们要学习如何利用时钟来完成时序逻辑。硬件说明流水灯实现是很常见的一个实验,虽然逻辑比较简单,但是里面也包含了实现时序逻辑的基本思想。要用FPGA实现流水灯有很多种方法,在这里我们会用两种不同的方法实现。1,模块化设计:在之前的实验中我们做了3-8译码器和时钟分频,如果把这两个结合起来,我们就能搭建一个自动操作的流水LED显示。框图如下:2,循环赋值:这是一种很简洁的实现流水灯效果逻辑,就是定义一个8位的变量,在每个时钟上升沿将最低位赋值给最高位,其他位右移一

关键字:

流水灯 FPGA Lattice Diamond 小脚丫

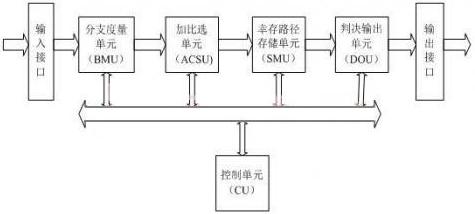

随着大模型、高性能计算、量化交易和自动驾驶等大数据量和低延迟计算场景不断涌现,加速数据处理的需求日益增长,对计算器件和硬件平台提出的要求也越来越高。发挥核心器件内部每一个计算单元的作用,以更大带宽连接内外部存储和周边计算以及网络资源,已经成为智能化技术的一个重要趋势。这使得片上网络(Network-on-Chip)这项已被提及多年,但工程上却不容易实现的技术再次受到关注。作为一种被广泛使用的硬件处理加速器,FPGA可以加速联网、运算和存储,其优点包括计算速度与ASIC相仿,也具备了高度的灵活性,能够为数据

关键字:

2D NoC FPGA

时钟分频在之前的实验中我们已经熟悉了小脚丫的各种外设,掌握了verilog的组合逻辑设计,接下来我们将学习时序逻辑的设计。====硬件说明====时钟信号的处理是FPGA的特色之一,因此分频器也是FPGA设计中使用频率非常高的基本设计之一。一般在FPGA中都有集成的锁相环可以实现各种时钟的分频和倍频设计,但是通过语言设计进行时钟分频是最基本的训练,在对时钟要求不高的设计时也能节省锁相环资源。在本实验中我们将实现任意整数的分频器,分频的时钟保持50%占空比。1,偶数分频:偶数倍分频相对简单,比较容易理解。通

关键字:

时序逻辑 时钟分频 FPGA Lattice Diamond 小脚丫

fpga 介绍

FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473