- 时间一晃又到了2014年的12月份,在辛苦工作了一年之后,大家都在等待着合家团圆,而IT行业也在酝酿着新的一年的改变。最新的消息是,AMD公司的“RedTeam”披露了其明年的APU和GPU规划,其中最引人注意的,自然是制程工艺的转变。然而外媒也指出,AMD的16纳米FinFET设计在2015年登陆主流市场并无望。

AMD首席技术官MarkPapermaster表示:“我公司的FinFET设计已经起步,但我们并不会是任何前沿技术的首个使用者”。换言

- 关键字:

AMD FinFET SoC

- 台积电昨(12)日宣布,完成16纳米主流制程FinFET+(鳍式场效晶体管强化版)全球首颗网通芯片及手机应用处理器试产,预定本月完成所有可靠性试验,明年7月正式量产。

这是台积电拓展先进制程一大里程碑。业界认为,正值三星再度与台积电争夺苹果下世代A9处理器订单之际,台积电16纳米FinFET+技术到位后,将进一步拉大与三星差距,对台积电而言,A9订单「有如探囊取物」,最快明年夏天开始投产A9芯片。

台积电昨天不对单一客户导入16纳米制程状况置评,强调明年底前,估计将完成近60件产品设计定案

- 关键字:

台积电 FinFET+

- 行动装置如智慧型手机、平板电脑等应用领域,对于半导体晶片的需求走到超低功耗,制程技术从28奈米制程,到20奈米制程,将于2015年进入第一代3D设计架构的FinFET制程,也就是14/16奈米世代。

台积电2015年下半即将量产16奈米世代,英特尔、三星电子(Samsung Electronics)、GlobalFoundries将是14奈米制程世代,英特尔早一些量产,之后是三星,GlobalFoundries制程技术将属于三星阵营。

台积电因为为大客户苹果生产20奈米制程晶片,因此16奈

- 关键字:

16纳米 FinFET

- 全球知名的电子设计创新领导者Cadence设计系统公司今日宣布其丰富的IP组合与数字和定制/模拟设计工具可支持台积电全新的超低功耗(ULP)技术平台。该ULP平台涵盖了提供多种省电方式的多个工艺节点,以利于最新的移动和消费电子产品的低功耗需求。

为加速台积电超低功耗平台的技术发展,Cadence将包括存储器、接口及模拟功能的设计IP迁移到此平台。使用Cadence TensilicaÒ数据平面处理器,客户可以从超低功耗平台受益于各种低功耗DSP应用,包括影像、永远在线的语音、面部识

- 关键字:

Cadence 台积电 FinFET

- 全球知名的电子设计创新领导者Cadence设计系统公司今日宣布为台积电16纳米FinFET+ 制程推出一系列IP组合。 Cadence所提供的丰富IP组合能使系统和芯片公司在16纳米FF+的先进制程上相比于16纳米FF工艺,获得同等功耗下15%的速度提升、或者同等速度下30%的功耗节约。

目前在开发16 FF+工艺的过程中,Cadence的IP产品组合包括了在开发先进制程系统单芯片中所需的多种高速协议,其中包括关键的内存、存储和高速互联标准。IP将在2014年第四季度初通过测试芯片测试。有关IP

- 关键字:

Cadence 台积电 FinFET

- 全球知名电子设计创新领先公司Cadence设计系统公司今日宣布,其数字和定制/模拟分析工具已通过台积电公司16FF+制程的V0.9设计参考手册(Design Rule Manual,DRM) 与SPICE认证,相比于原16纳米FinFET制程,可以使系统和芯片公司通过此新工艺在同等功耗下获得15%的速度提升、或者在同等速度下省电30%。目前16FF+ V1.0认证正在进行中,计划于2014年11月实现。Cadence也和台积电合作实施了16FF+ 制程定制设计参考流程的多处改进。此外,Cadence也

- 关键字:

Cadence 台积电 FinFET

- 全球知名电子设计创新领先公司Cadence设计系统公司,今日宣布台积电采用了Cadence®16纳米FinFET单元库特性分析解决方案。由Cadence和台积电共同研发的单元库分析工具设置已在台积电网站上线,台积电客户可以直接下载。该设置是以Cadence Virtuoso® Liberate® 特性分析解決方案和Spectre® 电路模拟器为基础,并涵盖了台积电标准单元的环境设置和样品模板。

利用本地的Spectre API整合方案,Liberate和Spect

- 关键字:

Cadence 台积电 FinFET

- 鳍式场效电晶体(FinFET)及三维积体电路(3DIC)引爆半导体业投资热潮。行动装置与物联网(IoT)市场快速成长,不仅加速半导体制程技术创新,晶圆厂、设备厂等业者亦加足马力转往3D架构及FinFET制程迈进,掀动半导体产业庞大的设备与材料投资风潮。

应用材料集团副总裁暨台湾区总裁余定陆表示,3DIC及FinFET制程将持续引爆半导体业的投资热潮,亦促使创新的设备材料陆续问世。

应用材料(AppliedMaterials)集团副总裁暨台湾区总裁余定陆表示,随着行动装置的功能推陈出新,及联

- 关键字:

FinFET 半导体

- 应用材料公司今天宣布全新推出Applied Varian VIISta® 900 3D系统。作为业内领先的中电流离子注入设备,该系统专为2x纳米以下节点的FinFET和3D NAND制程而开发,具有超凡的控制能力,可以帮助高性能、高密度的复杂3D器件实现器件性能优化,降低可变性,提高良率,是应用材料公司在精密材料工程领域的又一重大突破。

VIISta 900 3D系统能有效提高离子束角度精度和束线形状准确度,并且还能够出色的控制离子剂量和均匀性,从而帮助客户实现制程的可重复性,优化器件性

- 关键字:

VIISta 900 3D 2x纳米 FinFET

- Needham & Co.半导体设备分析师Edwin Mok 27日针对晶圆代工领域提出了透彻分析,认为相关的半导体设备订单有望在今(2014)年下半年攀高,但16/14奈米FinFET(鳍式场效电晶体)订单却将递延一季。

barron`s.com报导,Mok发表研究报告指出,据了解晶圆代工厂格罗方德(GlobalFoundries;GF)正在提高纽约州Malta厂的20奈米制程产能,而三星电子(Samsung)也正在逐渐增加Austin厂的设备,这似乎支持了近来传出的高通(Qualco

- 关键字:

FinFET 14纳米

- 应用材料公司(AppliedMaterials)宣布其全新EnduraVolta化学气相沈积(CVD)系统加入独特的钴金属后,一举突破导线技术传统瓶颈,让“摩尔定律”持续向下进展到20纳米。此外,应材的EnduraVentura实体气相沈积(PVD)系统不但成功协助客户降低成本,更可制造出体积更小、耗能更低、性能更高的整合型3D芯片。

在强大技术创新突破的支持下,应用材料公司在营运方面也颇有斩获。应用材料公司台湾区总裁余定陆表示,拜半导体事业的蓬勃发展与应用材料公司不

- 关键字:

应用材料 FinFET

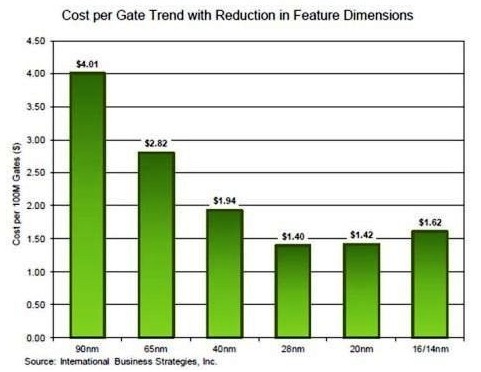

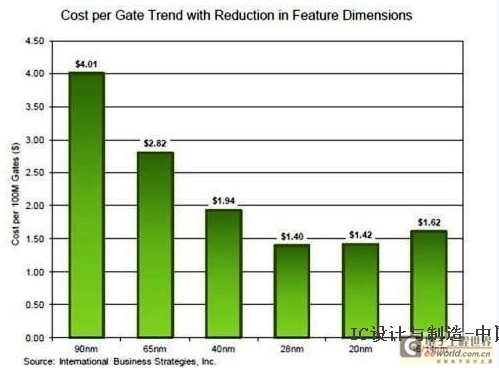

- 在历史上,半导体产业的成长仰赖制程节点每一次微缩所带来的电晶体成本下降;但下一代晶片恐怕不会再伴随着成本下降,这将会是半导体产业近20~30年来面临的最严重挑战。

具体来说,新一代的20奈米块状高介电金属闸极(bulk high-K metal gate,HKMG) CMOS制程,与16/14奈米 FinFET 将催生更小的电晶体,不过每个逻辑闸的成本也将高出目前的28奈米块状HKMG CMOS制程。此成本问题部分源自于在新制程节点,难以维持高参数良率(parametric yields)以及低

- 关键字:

FinFET 半导体

- 在历史上,半导体产业的成长仰赖制程节点每一次微缩所带来的电晶体成本下降;但下一代晶片恐怕不会再伴随着成本下降,这将会是半导体产业近20~30年来面临的最严重挑战。

具体来说,新一代的20奈米块状高介电金属闸极(bulk high-K metal gate,HKMG) CMOS制程,与16/14奈米 FinFET 将催生更小的电晶体,不过每个逻辑闸的成本也将高出目前的28奈米块状HKMG CMOS制程。此成本问题部分源自于在新制程节点,难以维持高参数良率(parametric yields)以

- 关键字:

FinFET 半导体

- 重点: · 认证确保精确性方面不受影响,并包含用于65纳米至14纳米FinFET制程的物理验证签收的先进技术 · 双方共同的客户可通过它与Cadence Virtuoso及Encounter平台的无缝集成进行版图设计和验证版图 全球电子设计创新领先企业Cadence设计系统公司今天宣布Cadence® Physical Verification System (PVS)通过了GLOBALFOUNDRIES的认证,可用于65纳米

- 关键字:

Cadence FinFET Virtuoso Encounte

- 大量的金钱和精力都花在探索FinFET工艺,它会持续多久和为什么要替代他们?

在近期内,从先进的芯片工艺路线图中看已经相当清楚。芯片会基于今天的FinFET工艺技术或者另一种FD SOI工艺的平面技术,有望可缩小到10nm节点。但是到7nm及以下时,目前的CMOS工艺路线图已经不十分清晰。

半导体业已经探索了一些下一代晶体管技术的候选者。例如在7nm时,采用高迁移率的FinFET,及用III-V族元素作沟道材料来提高电荷的迁移率。然后,到5nm时,可能会有两种技术,其中一种是环栅F

- 关键字:

晶体管 FinFET

finfet介绍

FinFET称为鳍式场效晶体管(FinField-effecttransistor;FinFET)是一种新的互补式金氧半导体(CMOS)晶体管,闸长已可小于25奈米,未来预期可以进一步缩小至9奈米,约是人类头发宽度的1万分之1。由于此一半导体技术上的突破,未来芯片设计人员可望能够将超级计算机设计成只有指甲般大小。 FinFET源自于目前传统标准的晶体管—场效晶体管 (Field-ef [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473