cadence 文章 进入cadence技术社区

Cadence 推出开拓性的 Virtuoso Studio

- · 这是一个业界用于打造差异化定制芯片的领先平台,可借助生成式 AI 技术显著提升设计生产力;· Virtuoso Studio 与 Cadence 最前沿的技术和最新的底层架构集成,助力设计工程师在半导体和 3D-IC 设计方面取得新突破;· 依托 30 年来在全线工艺技术方面取得的行业领先

- 关键字: Cadence Virtuoso Studio

Cadence 加强其 Tensilica Vision 和 AI 软件合作伙伴生态

- 新加入的生态系统成员包括 Kudan 和 Visionary.ai,有助于快速部署高性能、高能效的基于 SLAM 和 AI ISP 的解决方案 中国上海,2023 年 4 月 12 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布欢迎 Kudan 和 Visionary.ai 加入 Tensilica 软件合作伙伴生态系统,他们将为 Cadence® Tensilica® Vision DSP 和 AI 平台带来业界领先的同步与地图构建 (SLAM)和 AI 图像

- 关键字: Cadence Tensilica Vision AI 软件

Cadence荣获六项2022 TSMC OIP年度合作伙伴大奖

- 内容提要:· Cadence 凭借关键的 EDA、云和 IP 创新荣获 TSMC 大奖;· Cadence 是 TSMC 3DFabric 联盟的创始成员之一。 中国上海,2022年12月14日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,其 EDA、IP 和云计算解决方案获得了 TSMC 颁发的六项 Open Innova

- 关键字: Cadence 2022 TSMC OIP

Cadence发布Verisium AI-Driven Verification Platform引领验证效率革命

- 楷登电子(美国 Cadence 公司)近日宣布,推出 Cadence® Verisium™ Artificial Intelligence (AI)-Driven Verification Platform,整套应用通过大数据和 JedAI Platform 来优化验证负荷、提高覆盖率并加速 bug 溯源。Verisium 平台基于新的 Cadence Joint Enterprise Data AI (JedAI) Platform,并与 Cadence 验证引擎原生集成。随着 SoC 复杂性不断提高,

- 关键字: Cadence Verisium AI-Driven Verification Platform 验证

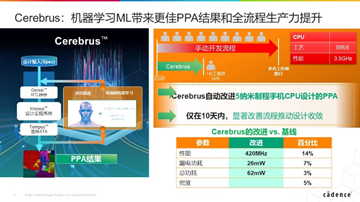

联发科与瑞萨采用Cadence Cerebrus AI方案 优化芯片PPA

- Cadence Design Systems, Inc.宣布,Cadence CerebrusÔ智能芯片设计工具(Intelligent Chip Explorer) 获得客户采用于其全新量产计划。此基于 Cadence Cerebrus 采用人工智能 (AI) 技术带来自动化和扩展数字芯片设计能力,能为客户优化功耗、效能和面积 (PPA),以及提高工程生产力。Cadence Cerebrus 运用革命性的AI技术,拥有独特的强化学习引擎,可自动优化软件工具和芯片设计选项,提供更好的 PPA进而大幅减少工

- 关键字: 联发科 瑞萨 Cadence Cerebrus AI 芯片PPA

大幅缩减设计进程 Cadence新设备为硬件仿真验证提速

- 当前随着国内IC设计产业越来越受关注,短时间内涌现出海量的IC设计初创企业,对这些初创或者正在快速成长的IC设计企业来说,如何尽可能缩短设计进程,加速设计上市时间是一个不可回避的关键点。作为当下几乎已经占据IC设计近60%工作量的仿真与验证环节,如果能够借助先进的工具大幅缩短这个过程所需的时间,那么将为诸多IC设计企业的产品成功增添重要的砝码。 为了更好地提升IC设计客户的仿真与验证效率,三大EDA公司不断更新各自的仿真验证工具,希望尽可能将该环节的时间大幅压缩,其中Cadence选择推出下一代

- 关键字: Cadence Palladium Z2 Protium X2 仿真验证

cadence介绍

EDA仿真软件Cadence

--------------------------------------------------------------------------------

Cadence Design Systems Inc.是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。其解决方案旨在提升和监控半导 [ 查看详细 ]