- 线网络是未来网络发展的趋势,除了硬设备的研发,软件的开发也是非常重要的一环。在目前的GPRS网络环境里,传输速度以及稳定度仍有着不足的地方,透过各种无线网络最佳化技术的实作,可提供个对于目前GPRS网络环境加速2~4倍的软件解决方案,也希 望借着这个解决方案的产生,让无线网络的领域更加宽广。

- 关键字:

Cache GPRS IP

- 以一款SPARC V8处理器为例,分析了处理器分级存储系统中Cache和MMU对断点调试实现的影响,提出有效的解决办法,并成功应用到该处理器的调试工具中。该方法也适用于其他具有Cache和MMU的处理器断点调试设计。

- 关键字:

SPARCV8处理器 cache MMU 断点调试

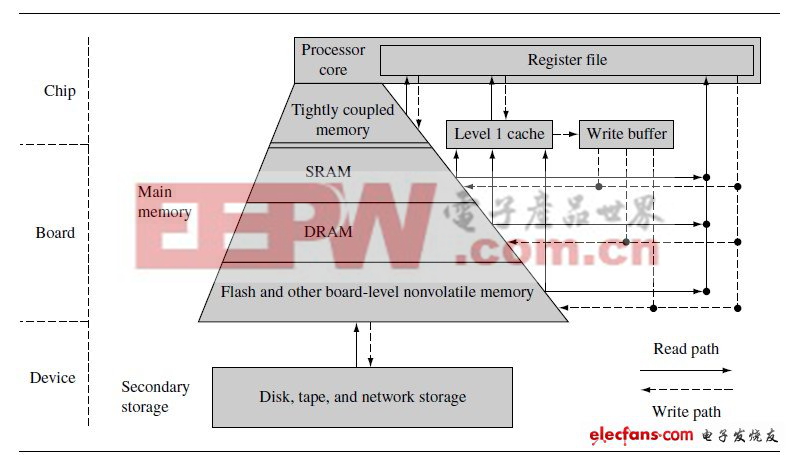

- 计算机系统一般都采用多级存储器结构,这种多级存储器的特点是从外存储器到CPU中的寄存器逐级向上,存储容量逐级减小,而存取速度逐级提高。Cache是一个速度等于或者接近上一级存储器访问速度的小容量存储器,其中保存了下级存储器中部分当前所需的数据,因此CPU可以直接从Cache中取得所需的数据,而不必访问下一级存储器。由于Cache的速度与上一级存储器相当,因此保证了系统效率不会降低。

- 关键字:

cache 系统效率 最近最少使用算法

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

ARM 高速缓冲存储器 cache

- linux dma cache,说到DMA,就会想到Cache,两者本身似乎是好不相关的事物。的确,假设DMA针对内存的目的地址和Cache缓存的对象没有重叠区域,DMA和Cache之间就相安无事,但是,如果有重叠呢,经过DMA操作,Cache缓存对应的内存的数据

- 关键字:

cache dma linux

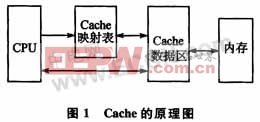

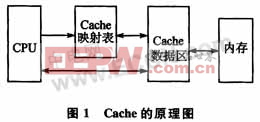

- 1 Cache的原理

Cache即高速缓存,它的出现基于两种因素:一、CPU的速度和性能提高很快,而主存速度较低且价格高;二、程序执行的局部性特点。将速度较快而容量有限的SRAM构成Cache,可以尽可能发挥CPU的高速度。

- 关键字:

需要 注意 问题 及其 原理 编程 Cache 嵌入式

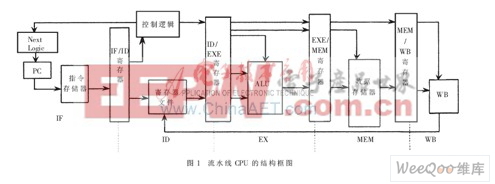

- 一种带Cache的嵌入式CPU的设计与实现,摘 要: 基于FPGA平台实现了嵌入式RISC CPU的设计。根据项目要求,实现指令集为MIPS CPU指令集的一个子集,分析指令处理过程,构建了嵌入式CPU的5级数据通路。分析了流水线产生的相关性问题,采用数据前推技术和软件

- 关键字:

实现 设计 CPU 嵌入式 Cache

- ARM核920T性能优化之Cache,程序在执行过程中会频繁的运行小范围的循环代码,而这些循环又会对数据存储器的局部区域反复访问。 Cache同时使用了时间和空间的局部性原理。如果对存储器的访问受时间影响,在时间上有连续性,则这种时间上密集的

- 关键字:

Cache 优化 性能 920T ARM

- 1 Cache的原理

Cache即高速缓存,它的出现基于两种因素:一、CPU的速度和性能提高很快,而主存速度较低且价格高;二、程序执行的局部性特点。将速度较快而容量有限的SRAM构成Cache,可以尽可能发挥CPU的高速度。

- 关键字:

及其 原理 机制 Cache 编程 注意 嵌入式

- 在分析Cache性能的基础上介绍了当前低功耗Cache的设计方法,提出了一种可重构Cache模型和动态可重构算法。Cache模型能够在程序运行过程中改变相联度和大小,动态可重构算法能够在运行时针对不同的应用程序对可重构Cache进行配置。通过对Cache的动态配置,不仅可以提高Cache命中率,还能够有效降低处理器的功耗。

- 关键字:

Cache 低功耗 可重构 技术研究

- 采用自顶向下的流程设计了一款32位DSP的cache。该cache采用两级结构,第一级采用哈佛结构,第二级采用普林斯顿结构。本文详细论述了该cache的结构设计及采用的算法。

- 关键字:

结构设计 cache 两级 DSP 32位

cache介绍

cache ,高速缓冲存储器,为一种特殊的存储器子系统,其中复制了频繁使用的数据以利于快速访问。存储器的高速缓冲存储器存储了频繁访问的 RAM 位置的内容及这些数据项的存储地址。当处理器引用存储器中的某地址时,高速缓冲存储器便检查是否存有该地址。如果存有该地址,则将数据返回处理器;如果没有保存该地址,则进行常规的存储器访问。因为高速缓冲存储器总是比主RAM 存储器速度快,所以当 RAM 的访问 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473