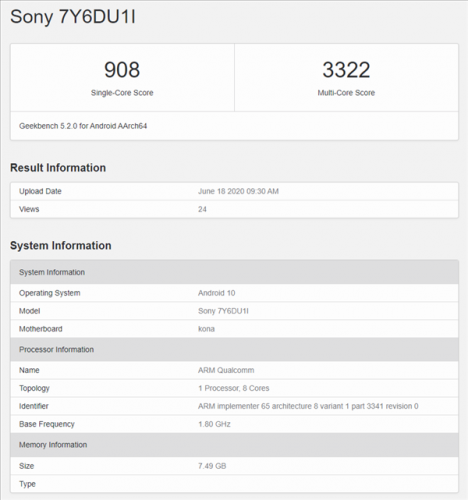

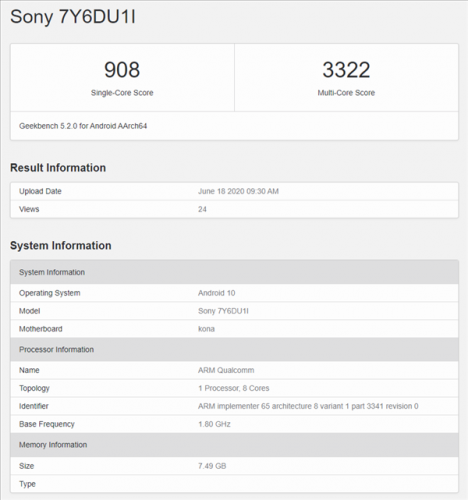

- 近日消息,型号为7Y6DU1I的索尼新机现身GeekBench跑分网站。如图所示,该机的单核成绩为908,多核成绩为3322,搭载高通骁龙865旗舰平台,配备8GB内存,运行Android 10。外媒猜测,这可能是索尼新一代旗舰Xperia 5 Ⅱ。之前索尼移动总裁Mitsuya Kishida在接受采访时透露,未来索尼移动旗舰将会沿用Ⅲ、Ⅳ这样的命名方式。由此看来,索尼Xperia 5的继任者将会命名为Xperia 5 Ⅱ。按照惯例,Xperia 5的继任者会在下半年登场,这款GeekBench网站刚刚

- 关键字:

Xperia 5 Ⅱ 索尼 骁龙865

- 索尼正式官宣了美版Xperia 1 Ⅱ的开售时间与价格,全球首款4K屏865机皇索尼Xperia 1 Ⅱ将于6月1日在美国开启预售,并于7月24日正式发货。 至于价格,只有8+256GB一个版本,售价1199.99美元,约合人民币8500元。 核心配置上,索尼Xperia 1 Ⅱ采用6.5英寸21:9 4K HDR OLED带鱼屏,分辨率为3840×1644,搭载高通骁龙865旗舰平台,配备8GB内存+256GB存储,前置800万像素,电池容量为4000mAh,支持IP68级防尘防水。 影像方面,索

- 关键字:

索尼 Xperia 1 Ⅱ

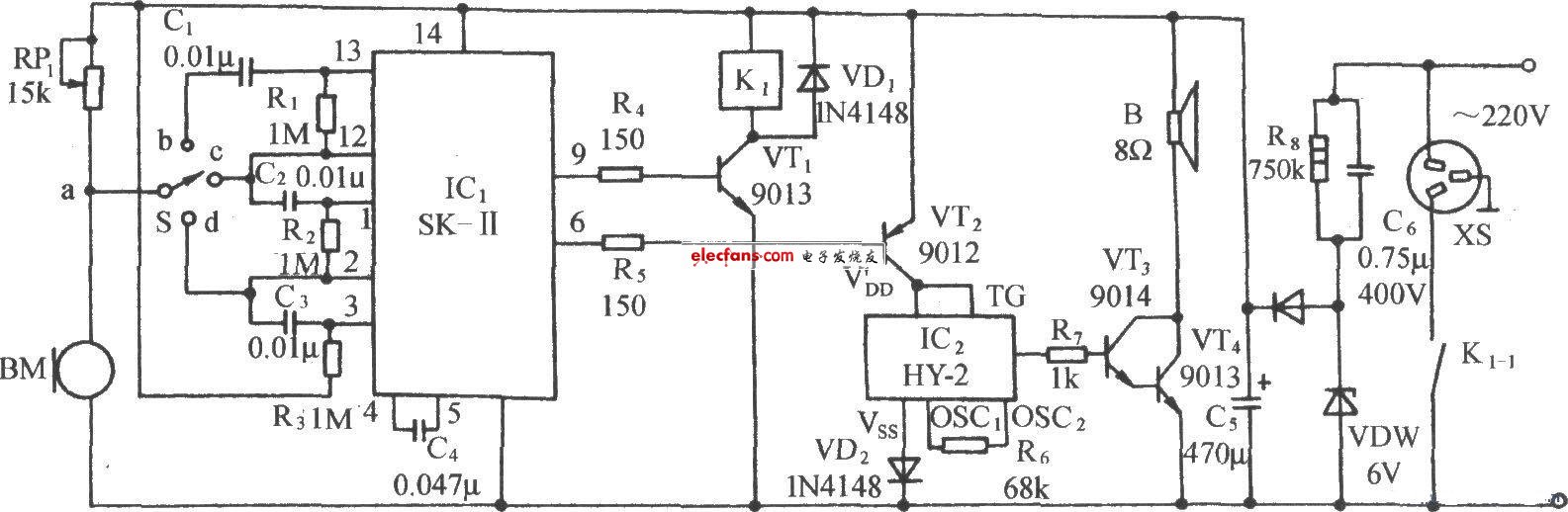

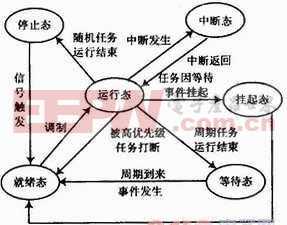

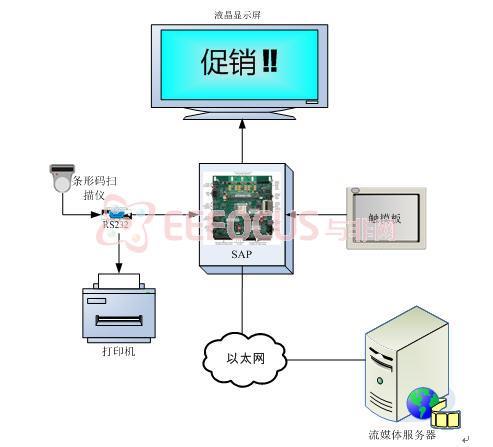

- 崔海朋青岛杰瑞工控技术有限公司(青岛266061) 摘 要:通过对塔式太阳能定日镜追日控制原理进行研究,提出了一种基于ARM Cortex-M3芯片的嵌入式跟踪控制器方案,主要包括模块化的硬件电路设计和µc/OS-Ⅱ嵌入式操作系统设计。该控制器具有太阳位置计算、信号采集处理、控制及以太网通讯等功能。该控制器在定日镜样机中进行验证,结果表明该控制器具有追踪精度高、环境适应性强、功耗低等特点,能满足塔式太阳能定日镜的跟踪要求。 关键词:塔式太阳能热发电;Cortex-M3;µc/OS-Ⅱ 0 引言

- 关键字:

201910 塔式太阳能热发电 Cortex-M3 µc/OS-Ⅱ

- 现场可编程逻辑门阵列(FPGA)和高性能数字信号处理器(DSP)是高速信号处理领域两大关键器件,FPGA和DSP的运算速度及并行处理效能成为制约高速信号处理应

- 关键字:

Virtex FPGA 嵌入式 信号处理

- 高频交易,这个名词可能对你并不陌生,它是指那些人们无法利用的,极为短暂的市场变化中寻求获利的自动化程序交易,高频交易瞬息万变,而决胜的关键就在于快。今天小编就给大家介绍一款Aldec最新的专门用于高频交易的PCIe卡,由小编前面的介绍,大家一定也只知道这款卡的主打性能就是速度快,没错,这也就不难理解为什么Aldec的新型的面向高频交易的HES-HPC-HET-XCVU9P PCIe卡采用Xilinx Virtex UltraScale + VU9P&n

- 关键字:

Virtex FPGA

- 随着以TD-SCDMA为代表的3G移动通信全面进入商用部署,LTE标准基本完成,华为、爱立信成功实现LTE标准的现场演示[1],以LTE-A、IMT-Advanced为标准的下一代移动通信技术

- 关键字:

Virtex-5FPGA Gbps 无线通信

- ISE设计套件11的全功能版本将作为Virtex-6 FPGA套件的一部分推出,器件支持仅限于Vitex-6 LX240T-FF1156。Spartan-6 FPGA 套件包括ISE设计套件11 WebPACK软件。ISE设计套件作为独立产品另外提供,可提供全面的器件支持,逻辑版本的起价为2995美元。客户可从赛灵思网站免费下载 ISE设计套件11的全功能30天评估版本。

- 关键字:

目标设计平台 Virtex-6 FPGA 系统开发

- 赛灵思公司在正式发布新一代旗舰产品高性能Virtex-6和低成本Spartan-6 FPGA时,首次提出了“目标设计平台”的新概念。赛灵思目标设计平台包含五个关键部分:Virtex-6和Spartan-6 FPGA器件、支持和集成业界成熟设计方法的设计环境、采用业界标准FPGA多层连接器的可扩展板和套件、提供接口的IP内核和强大的参考设计。

- 关键字:

目标设计平台 系统开发 FPGA Virtex-6 Spartan-6

- 本应用指南阐述了如何设计面向 Virtex?芯片的功率分配系统。涵盖了功率分配系统和旁路电容或去耦电容的基本原理。文中介绍了设计和验证功率分配系统的具体步骤和过程。最后一个部分讨论了产生电源噪声的其他原因,并提出了解决方案。

- 关键字:

Virtex-II系列 应用指南 FPGA

- 基于最大似然 (ML)估计算法,改进并利用FPGA实现了一种适用于TD-LTE系统的上行同步算法。主要介绍了如何利用FPGA实现ML算法。并以Virtex-5芯片为硬件平台,进行了仿真、综合、板级验证、联机验证等工作。结果表明,该同步算法应用到TD-LTE系统具有良好的稳定性和可行性。

- 关键字:

TD-LTE Virtex-5 FPGA

- 随着技术研究与提案工作的进行,基站系统的研发也已经开始。本文研究工作依托于国家“863”计划Gbps 无线传输关键技术与试验系统研究开发项目,研制面向LTE-A、IMT-Advanced等未来移动通信标准,能够验证相关技术并达到标准技术指标的新型移动通信基站原型。

- 关键字:

无线通信基站 算法链路 Virtex

- 逻辑优化、逻辑布局和最小化互连延迟都是实现最大性能的重要工作。时序驱动综合技术对设计性能提供了重大改进。影响时序驱动综合的限制因素是估计布线延迟的精度。

- 关键字:

物理综合 最小化互连延迟 Virtex

virtex-Ⅱ介绍

您好,目前还没有人创建词条virtex-Ⅱ!

欢迎您创建该词条,阐述对virtex-Ⅱ的理解,并与今后在此搜索virtex-Ⅱ的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473