- 为了管理中断请求的优先级并处理其他异常,Cortex-M0处理器内置了嵌套中断控制器(NVIC)。NVIC的一些可编程控制器控制着中断管理功能,这些寄存器被映射到系统地址空间里,它们所处的区域被称为系统控制空间(SCS)。 NVIC有以下特性: 灵活的中断管理; 支持嵌套中断; 向量化的异常入口 中断屏蔽 灵活的中断管理 Cortex-M0处理器中,每一个外部中断都可以被使能或者禁止,并且可以被设置为挂起状态或者清除状态。处理器的中断可以是信号级的(在中断服务程序清除中断请求以前,外设的

- 关键字:

Cortex-M0 NVIC

- //====================================================// STM32 中断与嵌套NVIC 快速入门// netjob 20 ...

- 关键字:

STM32 中断与嵌套 NVIC

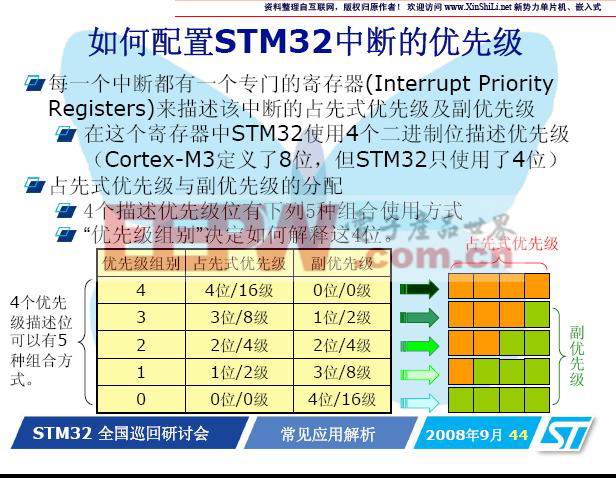

- STM32 (Cortex-M3) 中NVIC(嵌套向量中断控制)的理解,一、STM32 (Cortex-M3) 中的优先级概念STM32(Cortex-M3)中有两个优先级的概念:抢占式优先级和响应优先级,也把响应优先级称作“亚优先级”或“副优先级”,每个中断源都需要被指定这两种优先级

- 关键字:

控制 理解 中断 向量 Cortex-M3 NVIC STM32

nvic介绍

您好,目前还没有人创建词条nvic!

欢迎您创建该词条,阐述对nvic的理解,并与今后在此搜索nvic的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473