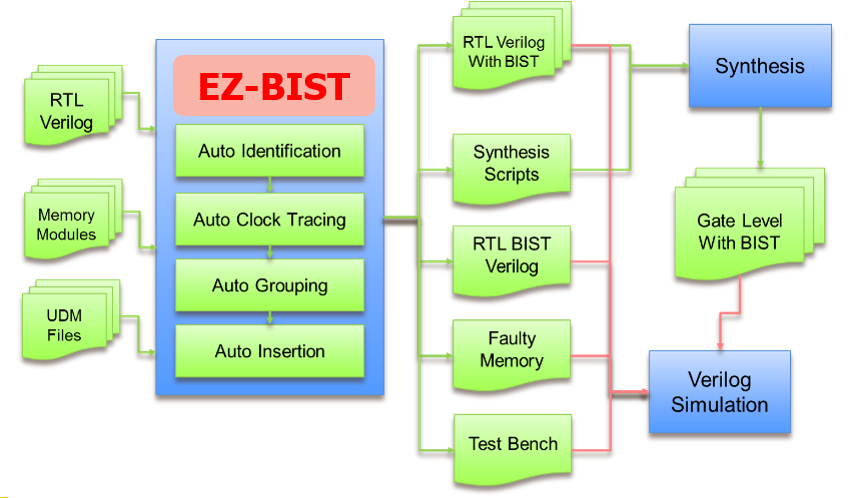

- 中美贸易战持续延烧,引发后续波及全球的贸易战争,当中更是突显知识产权合法的重要性。有鉴于此,深耕于开发内存测试与修复技术的芯测科技(iSTART-Tek,简称iSTART)为了协助客户对知识产权领域规避严重失信的风险,日前推出最新便捷版内存内建式自我测试(MBIST)测试方案「EZ-BIST」,适用于MCU相关的系统芯片开发商。采用芯测科技(iSTART)所提供低成本且高效率的内存测试开发工具,可协助客户快速的开发产品,避免忽略内存测试的细节而导致产品良率下降,而其适用的应用如触控屏、指纹辨识、语音识

- 关键字:

芯测 EZ-BIST

- 现场可编程门阵列(Field Programmable Gate Array, FPGA)是基于SRAM的一种硬件电路可重配置电子逻辑器件,可通过将硬件描述语言编译生成的硬件配置比特流编程到FPGA中,而使其硬件逻辑发生改变。

- 关键字:

FPGA SRAM MIPS 存储器 BIST

- Mentor Graphics公司(纳斯达克代码:MENT)日前宣布瑞萨电子正在使用Tessent® TestKompress®/LogicBIST混合解决方案,以应对ISO 26262标准规定的对安全很重要的测试要求。这种混合方法要求的测试逻辑非常少,从而提供完整的解决方案:既包括用于实现低每百万缺陷数量(DPM)的高压缩率扫描测试、又有内置自检(BIST)。

- 关键字:

瑞萨 Mentor BIST

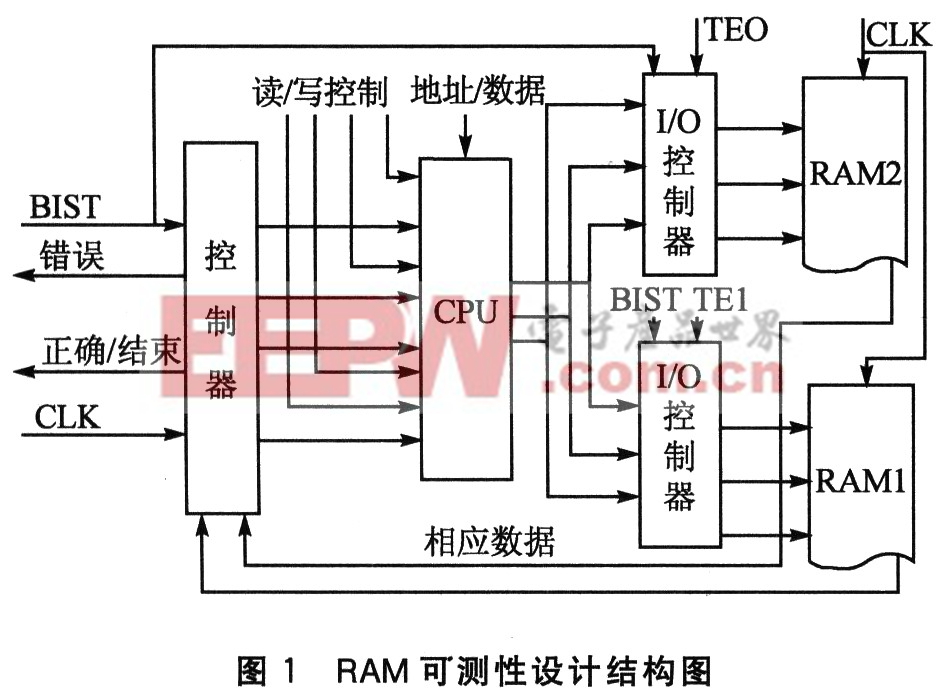

- 1 引言 随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合为一个系统,提高了设计效率,加快了设计过程,缩短了产品上市时间。但是随着设

- 关键字:

BIST IP核 测试 方案设计

- 引言 数字BIST的工作原理:用一个LFSR(线性反馈移位寄存器)生成伪随机的位模式,并通过临时配置成串行移位 ...

- 关键字:

BIST 基本原则

- 1 引言 随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合为一个系统,提高了设计效率,加快了设计过程,缩短了产品上市时间。但是随着设

- 关键字:

BIST IP核 测试方案

- 引言 大多数IC设计工程师都了解数字BIST的工作原理。它用一个LFSR(线性反馈移位寄存器)生成伪随机的位模式,并通过临时配置成串行移位寄存器的触发器,将这个位模式加到待测电路上。数字BIST亦用相同的触发器

- 关键字:

BIST 模拟

- 1 引言 随着半导体工艺的发展,片上系统SOC已成为当今一种主流技术。基于IP复用的SOC设计是通过用户自定义逻辑(UDL)和连线将IP核整合为一个系统,提高了设计效率,加快了设计过程,缩短了产品上市时间。但是随着设

- 关键字:

BIST 编译码器 IP核 测试

- BIST在SoC片上嵌入式微处理器核上的应用,介绍了SoC片上嵌入式微处理器核的一种测试技术――片内测试(BIST)。讲述了片上系统的由来以及两个重要特点。与传统的测试方法比较后,讨论了MereBIST、LogicBIST等常用BIST测试技术的结构和特点,分析了这几种测试方法的优缺点。

- 关键字:

应用 微处理器 嵌入式 SoC BIST

- 在BIST(内建自测试)过程中,线性反馈移位寄存器作为测试矢量生成器,为保障故障覆盖率,会产生很长的测

试矢量,从而消耗了大量功耗。在分析BIST结构和功耗模型的基础上,针对test―per―scan和test―per―clock两大BIST类型,介绍了几种基于LFSR(线性反馈移位寄存器)优化的低功耗BIST测试方法,设计和改进可测性设计电路,研究合理的测试策略和测试矢量生成技术,实现测试低功耗要求。

- 关键字:

LFSR BIST 低功耗设计

- 美国加州圣荷塞,芯片设计解决方案供应商微捷码(Magma®)设计自动化有限公司日前宣布,公司已向领先的半导体内置自测(BIST)和诊断解决方案提供商LogicVision公司提供了自动测试向量生成(ATPG)技术的授权。通过这项协议,LogicVision公司将能够更快拓展产品组合,为客户提供更全面的可测性设计(DFT)功能以改善测试质量、缩短纳米IC设计周期并降低纳米IC成本。此外,两家公司还签署了一份单独协议

- 关键字:

微捷码 BIST ATPG DFT IC

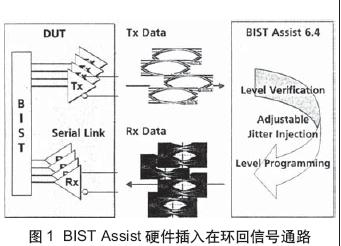

- 多年来,宽同步并行总线一直是在数字设备之间交换数据的既定的实现技术。但是,定时问题一直“折磨着”较高时钟频率和数据速率的并行总线,严重地限制了它们满足服务器和图形系统中更高速计算结构需求的能力。在过去几年中,串行总线技术的普遍实施变革了计算行业。串行总线只发送一条码流,“自行获得时钟输入”,从而消除了与并行技术有关的定时偏移。在串行传输中,同步远不是什么问题,解决了对整体吞吐量的结构限制。结果,串行数据速率已经提高到1Gb/s以上,当前实现方案已经接近3

- 关键字:

AWG BIST 串行

- 消费类电子产品正在变得更复杂和更快速,因而使得测试成本成为问题。大的和复杂的SoC往往是消费类产品的心脏,不管它们的性能多么先进,其成本必须是低的。

各种内装自测试(BIST)已应用于测试DUT(被测器件)的内部性能,导致产品较低的生产成本。剩下的主要问题是快速串行接口(如PCI Express,Serial ATA,FibreChannel和Serial RapidIO)的全面测试。这些高速链路在计算、通信和音视频娱乐前进中是不可缺少的。

重视测试成本是一个重要的问题,设计人员已应用BI

- 关键字:

BIST DUT

bist介绍

您好,目前还没有人创建词条bist!

欢迎您创建该词条,阐述对bist的理解,并与今后在此搜索bist的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473