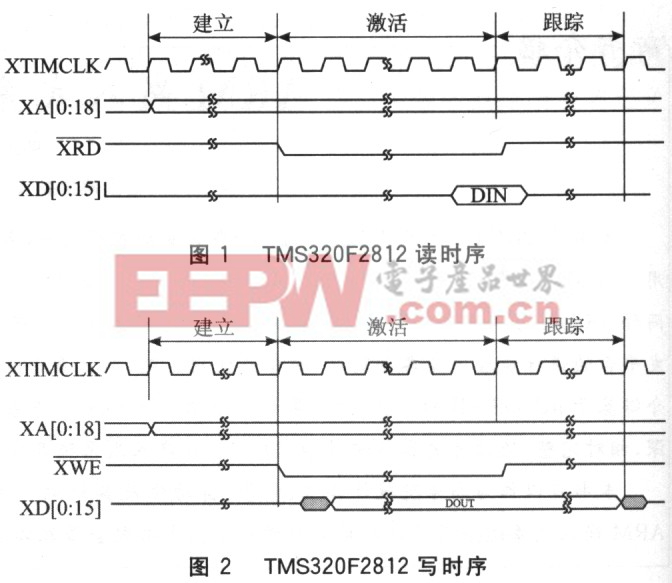

- TMS320F2812慢速外设接口的时序控制,TMS320F2812通常能够实现与常用外围芯片的时序匹配,如RAM、D/A等;但是,当遇到读、写周期十分缓慢的输入/输出设备,如液晶显示模块、打印机、键盘时,就需要设计相应的外部硬件等待电路。本文对定点DSP芯片的外部接

- 关键字:

时序 控制 接口 外设 慢速 TMS320F2812

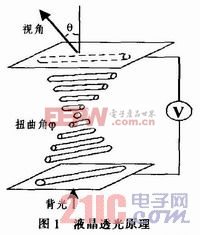

- 摘要:阐述了TFT-LCD的显示原理、系统结构和时序控制器TCON的设计方案。该模块设计主要为减少中、小尺寸TFT-LCD时序控制器的芯片管脚数,提高通用性,与一般TCON只能驱动2~3种分辨率的面板相比较,该设计支持8种显示

- 关键字:

设计 研究 TCON 控制器 时序

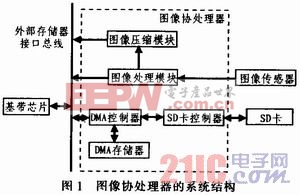

- 摘要:在以SD卡为图像存储器件的图像协处理器中,基带芯片和SD卡控制器在速度上的差异经常会导致数据传输错误。为解决此问题,设计了一种可适应多种时序情况的DMA控制器。该DMA控制器的状态机,一方面对基带芯片和SD

- 关键字:

控制器 设计 DMA 情况 多种 时序 适应

- 时序关联/质理检验方针助缩短开发周期,在工程的世界里,决定往往源自于深层分析。简单的决定可能需要几天、几周、甚至几个月的缜密研究。不信问下你的工程师朋友,听听他(她)在决定买哪台摄像机或笔记本电脑上花了多少时间,很可能他(她)花在研究产品规格

- 关键字:

开发 周期 缩短 方针 关联 检验 时序

- 在您决定哪种转换器最为适合于您的应用时,您可能会首先想到速度、精确度以及未来系统的可重复性。好吧,这都没问题,但请不要局限于这些显而易见的东西。一封来自 Harvey Wiggins 的电子邮件谈及了让一组 Delta;-

- 关键字:

时序 精确度

- 本文分析了IL-E2型TDI-CCD 芯片的工作过程和对驱动信号的要求,在此基础上设计出合理的时序电路, 为了满足在实际工作中像移速度异速匹配的要求,在时序电路的设计中时序发生部分是可调的。这种设计方案简单、可靠、实用。

- 关键字:

FPGA CCD 相机 时序

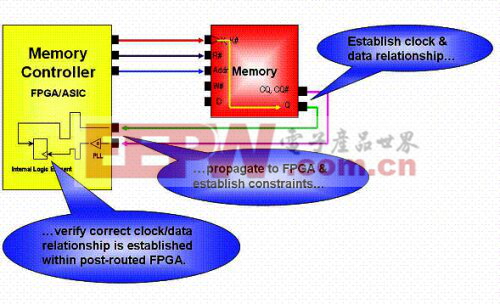

- FPGA设计中的时序管理, 当FPGA设计面临高级接口的设计问题时,该采取什么办法来解决呢?美国EMA公司的TimingDesigner软件可以简化这些设计问题,并提供对几乎所有接口的预先精确控制。下问文将向你娓娓道来。 一、摘要 从简单SRAM接

- 关键字:

管理 时序 设计 FPGA

- LT156是时序控制专用集成电路,它内部含有两个功能不同的独立部分,即计数,时序译码输出和低频振荡器.计数,译码部分能按时钟脉冲顺序依次驱动四组外电路.低频振荡器则带有使能

- 关键字:

应用 电路图 电路 控制 时序 LT156

- FPGA时序收敛,您编写的代码是不是虽然在仿真器中表现正常,但是在现场却断断续续出错?要不然就是有可能在您使用更高版本的工具链进行编译时,它开始出错。您检查自己的测试平台,并确认测试已经做到 100% 的完全覆盖,而且所有测试

- 关键字:

收敛 时序 FPGA

- SOC时序分析中的跳变点, 跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这在SOC设计后期,也就是要对时序签字时可能会导致问

- 关键字:

分析 时序 SOC

- 一般来说,LCD 模块的控制都是通过 MCU 对 LCD 模块的内部寄存器、显存进行操作来最终完成的;在此我们设计了三个基本的时序控制程序,分别是: 写寄存器函数(LCD_RegWrite) 数据写函数(LCD_DataWrite)

- 关键字:

驱动 编写 底层 时序 单片机 LCD 基于

- 为了探索多输入时序逻辑电路的简便实现方法,介绍了基于数据选择器和D触发器的多输入时序逻辑电路设计技术。即将D触发器和数据选择器进行组合,用触发器的现态作为数据选择器选择输入变量、数据选择器的输出函数作为触发器的D输入信号,构成既有存储功能又有数据选择功能的多输入端时序网络。由触发器的现态选择输入变量、所选择的输入变量决定触发器的次态转换方向。该方法适合实现互斥多变量时序逻辑电路,且在设计过程中不需要进行函数化简。

- 关键字:

时序 电路设计 输入 触发器 数据 选择 基于 收发器

- 介绍了基于MSI可编程计数器74Lsl61的时序逻辑电路设计技术,目的是探索MSI可编程计数器实现一般时序逻辑电路的扩展应用方法,即以计数器Q3,Q2,Q1,Q0端的代码组合表示时序逻辑电路的各个状态,由输入变量控制计数器的EP,ET及端,综合利用计数、置数、保持功能,使计数器的状态变化满足所要求的时序,用计数功能实现“次态=现态+1”的二进制时序关系,用置数功能实现“次态=预置数”的非二进制时序关系,用保持功能实现“次态=现态”的自循环时序关系。所述方法的创新点是提出了MSI可编程计数器改变应用方向的逻

- 关键字:

逻辑 电路设计 时序 计数器 可编程 基于

- 本文讨论一个高性能时钟发生器如何配合一个或多个集成收发器工作,以便简化整体设计、降低复杂度和成本,同时实现出色的系统接收和发射性能。即使基站长时间丢失时序参考信号,网络中的所有其他基站仍能保持同步。

- 关键字:

MIMO NxN 基站 时序

时序介绍

您好,目前还没有人创建词条时序!

欢迎您创建该词条,阐述对时序的理解,并与今后在此搜索时序的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473