- 在特权的上篇博文《基于FPGA的跨时钟域信号处理——专用握手信号》中提出了使用专门的握手信号达到异步时钟域数据的可靠传输。列举了一个简单的由请求信号req、数据信号data、应答信号ack组成的简单握手机制。riple兄更是提出了req和ack这两个直接的跨时钟域信号在被另一个时钟域的寄存器同步时的亚稳态问题。这个问题估计是整个异步通信中最值得探讨和关注的。

很幸运,特权同学找到了很官方的说法——《Application Note42:Metast

- 关键字:

FPGA 亚稳态

- 图3.27所示的是一个观察D触发器亚稳态的电路图。使用这个电路至少需要一个双通道示波器。 CLKA的波形是一个方波,通过R1与C1和C2的两个支路被延迟。如果将R1的触点向DATA输出方向进行调整,CLK的输出延迟会达到最大

- 关键字:

如何测量 亚稳态

- 图3.27所示的是一个观察D触发器亚稳态的电路图。使用这个电路至少需要一个双通道示波器。 CLKA的波形是一个方波,通过R1与C1和C2的两个支路被延迟。如果将R1的触点向DATA输出方向进行调整,CLK的输出延迟会达到最大

- 关键字:

亚稳态 测量方法

- 什么是亚稳态 在FPGA等同步逻辑数字器件中,所有器件的寄存器单元都需要预定义信号时序以使器件正确地捕获数据,进而产生可靠的输出信号。当另一器件将数据发送给FPGA时,FPGA的输入寄存器必须在时钟脉冲边沿前

- 关键字:

IDDR 亚稳态 方案

- 图3.29是一个简化的数字触发器原理图。在这个例子中,为放大器提供了对称的正、负电压。正反馈电路把电容C上的任何正电压驱动到电源正电压,或者把电容C上的任何负电压驱动到电源负电压。当用时钟驱动时,电路会稳定

- 关键字:

数字触发器 原理 亚稳态

- 如图3.30所示,采用ACTEL ACT-1门阵列实现的电路,当输入电压变化时,其输出产生脉冲的概率有多大?简单应用同步逻辑理论,它永远也不会发生。但现在我们会更好地理解这个问题了。首先检查最坏情况下建立时间:TPD=9

- 关键字:

亚稳态 错误率 分析

- 图3.27所示的是一个观察D触发器亚稳态的电路图。使用这个电路至少需要一个双通道示波器。CLKA的波形是一个方波,通过R1与C1和C2的两个支路被延迟。如果将R1的触点向DATA输出方向进行调整,CLK的输出延迟会达到最大值

- 关键字:

测量 亚稳态 方法

- 什么是亚稳态 在FPGA等同步逻辑数字器件中,所有器件的寄存器单元都需要预定义信号时序以使器件正确地捕获数据,进而产生可靠的输出信号。当另一器件将数据发送给FPGA时,FPGA的输入寄存器必须在时钟脉冲边沿

- 关键字:

IDDR 亚稳态 方案

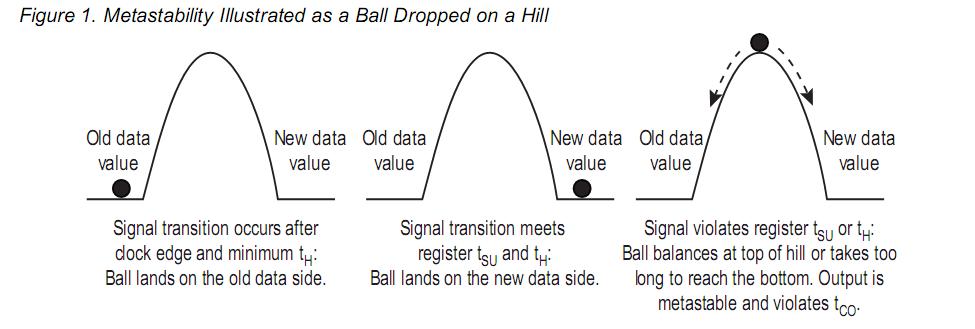

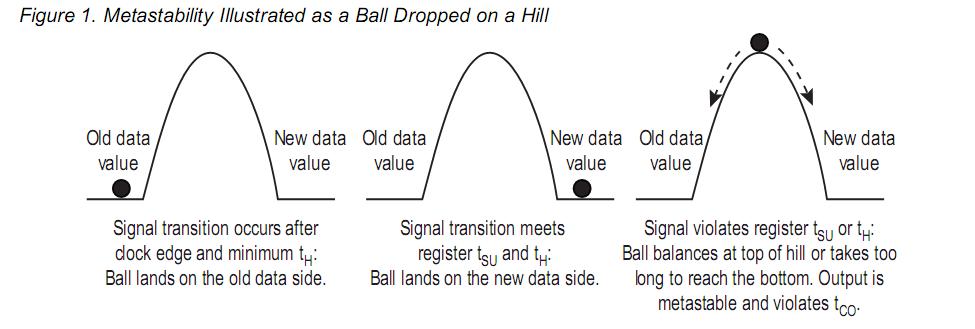

- 在FPGA等同步逻辑数字器件中,所有器件的寄存器单元都需要预定义信号时序以使器件正确地捕获数据,进而产生可靠的输出信号。当另一器件将数据发送给FPGA时,FPGA的输入寄存器必须在时钟脉冲边沿前保证最短的建立时间和时钟脉冲边沿后的保持时间,从而确保正常完整地 接收信号。

- 关键字:

IDDR 亚稳态

- 如图3.30所示,采用ACTEL ACT-1门阵列实现的电路,当输入电压变化时,其输出产生脉冲的概率有多大?简单应用同步逻辑理论,它永远也不会发生。但现在我们会更好地理解这个问题了。首先检查最坏情况下建立时间:TPD=9

- 关键字:

亚稳态 错误率 分析

- 图3.29是一个简化的数字触发器原理图。在这个例子中,为放大器提供了对称的正、负电压。正反馈电路把电容C上的任何正电压驱动到电源正电压,或者把电容C上的任何负电压驱动到电源负电压。当用时钟驱动时,电路会稳定

- 关键字:

数字触发器 原理 亚稳态

- 在现代IC设计中,特别是在模块与外围芯片的通信设计中,多时钟域的情况不可避免。当数据从一个时钟域传递到另一个域,并且目标时钟域与源时钟域不相关时,这些域中的动作是不相关的,从而消除了同步操作的可能性,并使系统重复地进入亚稳定状态[1]。在有大量的数据需要进行跨时钟域传输且对数据传输速度要求比较高的场合,异步FIFO是一种简单、快捷的解决方案。

异步FIFO用一种时钟写入数据,而用另外一种时钟读出数据。读写指针的变化动作由不同的时钟产生。因此,对FIFO空或满的判断是跨时钟域的。如何根据异步的指针

- 关键字:

FIFO 异步 Verilog HDL IC 亚稳态

亚稳态介绍

您好,目前还没有人创建词条亚稳态!

欢迎您创建该词条,阐述对亚稳态的理解,并与今后在此搜索亚稳态的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473