基于赛灵思FPGA的数字频域干扰抵消器

WCDMA同步算法

本文引用地址:http://www.eepw.com.cn/article/99723.htm对于任何一个系统,要进行正常的运作都必须首先保证系统的同步。WCDMA的小区搜索分为三个阶段,即主同步、辅同步和导频搜索三个阶段[5]。主同步利用PSC码对接收到的主同步信道数据(PSCH)做相关,根据相关峰值的位置确定时隙头。在主同步完成之后,辅同步阶段可以确定帧头位置和当前小区使用的扰码组号。方法是用辅同步码(SSC)去做相关。最后一个阶段是导频搜索,利用已经得到的扰码组号和帧头信息,遍历一个主扰码组所有的8个可能主扰码,分别和导频信道(CPICH)做相关。根据最大的相关值最终确定扰码号。可见,经过WCDMA的三步同步,就可以得到当前小区的主扰码号和帧同步信息。三步同步的流程图如图4所示。

由于同步模块收到的信号为4采样的,而同步模块内部的搜索过程只需利用单采样的数据,因此先要对过采样的信号进行下采样。另外,为了对发送信号源进行匹配,将接收到的信号首先经过根号升余弦匹配滤波器,然后再下采样到码片速率,如B点所示。

仿真和测试结果

仿真结果

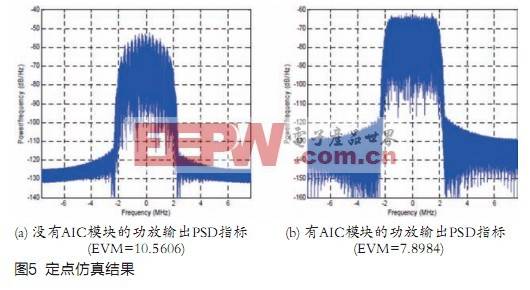

首先,经过功率谱密度图(PSD)验证,经过AIC的输出信号PSD曲线和发送信源PSD曲线基本一致。图5给出了信干比为-10dB时算法的定点仿真结果。

具体而言,在没有AIC的情况下,输出信号频谱主瓣内的波动较大,而且主瓣下降dB值减小。采用AIC后,输出信号频谱主瓣内的波动基本得以改善,并且下降dB值也基本等于原来输入信源的下降dB值,表明AIC性能良好。

WCDMA文章专题:WCDMA是什么意思

评论