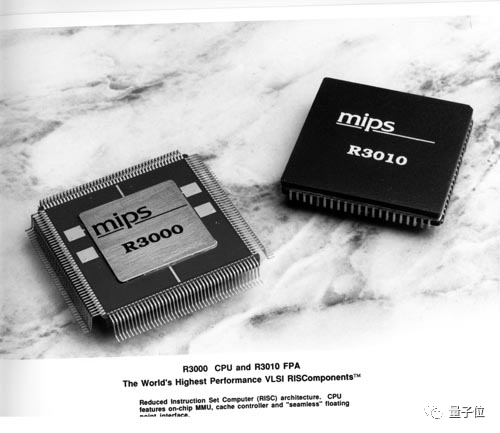

Open-Silicon、MIPS和Virage Logic共同完成ASIC处理器设计

Open-Silicon、业界标准处理器架构与内核领导厂商 MIPS 科技公司和Virage Logic 三家公司共同宣布,已成功开发一款测试芯片,充分展现出构建高性能处理器系统的业界领先技术。该处理器测试芯片实现了1.1GHz的频率速度,成功通过了65nm 芯片测试,使其成为65nm ASIC 中最快的处理器之一。同时,后续40nm器件的开发工作也已经开始进行,目标是超过2.5GHz频率,并提供超过5000 DMIPS的性能。这项开发计划采用了Open-Silicon的CoreMAXTM技术,以及超标量MIPS32 74K 处理器内核。74K是一款完全可合成的处理器内核,已广泛用于高端数字消费设备、机顶盒及网络解决方案。

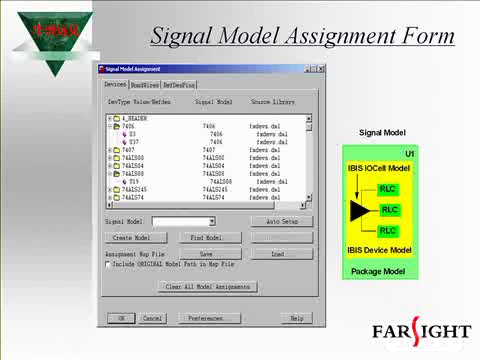

本文引用地址:http://www.eepw.com.cn/article/99544.htm该65nm测试芯片展现了这三家公司拥有可达到最高性能的标准ASIC构建的技术能力。74K处理器内核具备32KB L1指令和数据高速缓存、512KB L2高速缓存以及系统和内存控制器模块,并采用台积电(TSMC)的65nm GP工艺及标准10轨(track)单元库和Virage Logic的SiWare Memory编译器。该芯片已成功以1.1GHz 速度运行。为达到该目标,设计中采用了Open-Silicon专利的CoreMAX性能增强技术。该技术有利于设计人员构建数百万个新的标准单元,专门来加速设计的关键路径。再加上先进的SiWare Memory编译器和三重(triple)Vt工艺选项,有助于最终设计在所有工艺的最差状况(worst-case)下1.1GHz频率的时序收敛,并仍保有标准ASIC的裕量(margins)。

Open-Silicon公司总裁兼首席执行官Naveed Sherwani博士表示:“Open-Silicon很荣幸能与MIPS科技和Virage Logic公司共同合作,以展现我们的性能优化技术。Open-Silicon的 CoreMAX已被50多个客户设计所采用,可提高10% 的性能,为客户带来市场竞争优势。这款采用高速MIPS 处理器以及主流TSMC标准单元库的设计,已达到新的性能水平,证明了Open-Silicon的技术实力。”

Virage Logic公司总裁兼首席执行官Alex Shubat博士表示:“十多年来,Virage Logic的嵌入式内存一直是高性能处理器设计的最佳IP选择。我们很兴奋能成为Open-Silicon和MIPS科技的可信赖的IP伙伴,为他们提供通过硅验证的高速内存技术,消除系统瓶颈,实现尽可能最高的性能。”

40nm 测试芯片目前正开发中,计划于2010年第一季度完成。它的目标性能非常高,频率有望超过2.5GHz,最高可实现超过5000 DMIPS的速度。该测试芯片将包含74K处理器内核的浮点版本,以及L2高速缓存、系统和内存控制器模块。

MIPS科技公司总裁兼首席执行官 John Bourgoin指出:“长期以来,MIPS 科技一直是处理器IP产业的性能领导厂商,并将以这些最新成就传承该传统。74K内核是DTV、IPTV、有线机顶盒、网络连接应用及其它需要高性能应用的首选CPU。通过与Open-Silicon和Virage Logic等业界领导厂商的共同合作,我们将持续以新技术推动性能提升。MIPS科技的客户将享有足够的处理器性能空间,以支持未来几年产品功能持续增强的需求。”

评论