浮点:用 FPGA 嵌入式处理器实现您的构想

在采用数值处理技术创建嵌入式应用时,通常以整数或定点表示法来确保算术运算尽量简单,这一点至关重要。因其不仅有助于使成本和功耗降至最低,而且还能尽可能地加速硬件部署。

本文引用地址:http://www.eepw.com.cn/article/99212.htmFPGA 非常适用于执行定点运算,并能在逻辑或基于软件或硬件处理器的实施方案中创建高度并行的数据路径解决方案。Virtex®-5 FPGA 产品系列中 FXT 系列的最新硬件处理器 Xilinx® PowerPC® 440 可提供超标量功能,让用户能够对器件编程,使其以高达 550 MHz 的时钟速率并行执行一个或两个定点运算。

尽管用户能通过对器件进行编程来执行大多数采用整数或定点算术的运算,但通常须重新运算并插入比例运算以确保计算结果足够精确。对于复杂运算而言,这不仅耗时,而且还会导致程序变为专用型且不可重用。理想的替代方法是采用标准浮点表示法来提供一种适用于多个应用的高动态范围。这样人们就无需修改算法即可获得适用于任何特定应用或操作环境的定点实施方案,也无需为随后的项目及应用而大范围地修改代码。

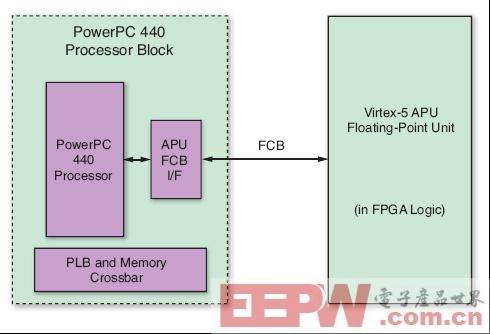

虽然赛灵思为基于 IBM 浮点性能库的 PowerPC 440 处理器提供了一种行之有效的仿真浮点解决方案,但处理器内核仍需占用数十个周期来执行每条运算。而采用浮点运算单元 (FPU) 形式的浮点运算硬件加速功能可缩短该运算周期。Virtex-5 FXT 系列中的 PowerPC 440 处理器提供了有效接口,能够将赛灵思软 FPU 等硬件加速器连接至该处理器内核。该方案可通过结构协处理器总线 (FCB) 将 PowerPC 440 处理器上的 128 位辅助处理器单元 (APU) 接口桥接至协处理器。使用该类协处理器(赛灵思 LogiCORE™ IP Virtex-5 APU-FPU),Virtex-5 FXT 用户可以选择软件仿真或者专用软逻辑 FPU 在 PowerPC 上自如地实现浮点运算。图 1 显示了通过 FCB 将 PowerPC 440 处理器连接至 Virtex-5 APU-FPU 的典型实施方案。

图 1——包含 APU-FPU 内核的嵌入式处理器系统

评论