基于Xtensa的ASIP开发流程研究

(1)将C++代码输入Tensilica Xplorer开发环境,选择系统自带的sample_config-params (RB-2006.0)配置信息作为ASIP开发的起点,即在此基础上进行体系结构的调整和指令的自定义开发。

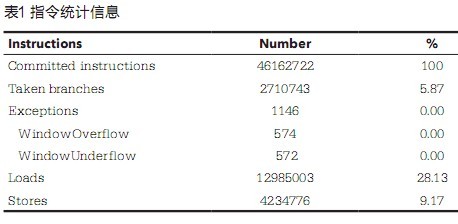

本文引用地址:http://www.eepw.com.cn/article/95269.htm(2) 运行代码并进行特性分析(Profile),表1和表2是最基本的指令和时钟周期信息,此外还可以得到pipeline甘特图、Branch cycle和Interlock cycle对比图等信息。这些信息为后续的体系结构调整和指令优化提供了必要的数据依据。

(3) 调整处理器配置信息中的众多项目,如MUL16 / MUL32 / MAC、Zero-overhead loop instructions、Pipeline length、Number of coprocessors、Floating point coprocessor、Special register、Cache size等,设计者可以得到图3所示的速度、面积、功耗信息。然后回到(2)再次运行代码及特性分析,考察体系结构改动带来的影响。

(4)利用XPRES工具,设置FLIX的Issue Width、SIMD的Vector Length、Register的Depth / Width / Ports、Fusion的Area / Latency / Operands等,XPRES会自动生成若干种不同的自定义指令TIE供设计者选择使用。设计者参考每一个TIE的Cycles和Gates数折衷考虑,当然设计者还可以手动增加TIE指令。然后将TIE绑定到调整后的体系结构(配置信息)上,回到(2)运行代码及特性分析,考察TIE带来的性能提高效果。

评论