基于Xtensa的ASIP开发流程研究

(1) 对处理器的体系结构进行配置的同时,设计者可以在Xplorer中实时看到每一次调整对ASIP性能产生的影响,如图3。

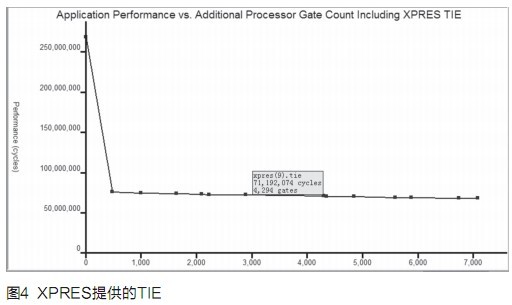

(2) XPRES工具可以完全自动地分析应用程序生成相应的指令扩展。设计人员只需输人利用标准ANSI C/C++设计的原始算法,XPRES便可以根据内置的配置选项完全自动化地产生多种TIE指令组合供设计者折中选择。

(3) 使用自定义的FLIX指令,它包括七种不同的64位指令字格式以及高达8个并行操作指令槽。FLIX提供VLIW风格的并行执行功能却没有VLIW处理器会发生的“代码膨胀”现象。

(4) XEnergy可以根据最终的体系结构配置和指令系统(包括设计者自定义的TIE扩展指令)评估ASIP功耗指标。

本项目目标是设计一款实现低功耗无损压缩的嵌入式ASIP。首先,经过比较从众多压缩算法中选择了简单高效的FELICS算法[11];然后开发算法的C++代码进行实际图像压缩实验。试验结果:FELICS对12幅目标图像的平均无损压缩比为2.7:1,满足本项目要求。之后的工作就是根据图2流程实现针对FELICS算法的ASIP设计。

评论