利用频域时钟抖动分析加快设计验证过程(07-100)

——

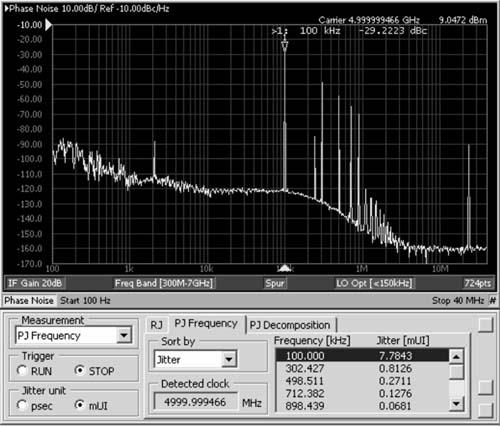

图6 相位噪声测量的PJ频率

通过先进的体系结构进行实时抖动测量

与传统的抖动测量模式不同,带有E5001A软件的E5052B SSA可以对相位噪声测量进行实时抖动分析。该仪器使用PLL提供参考源。它能够自动检测时钟频率,在几毫秒内把内置参考源自动调谐为时钟频率,测量相位检波器保持PLL所产生的噪声信号。它在250 MSa/s ADC上捕获噪声信号,从而可以进行100 MHz抖动带宽测量。该测量涵盖OC-192抖动分析范围。实时FFT可以获得频域数据,并能显著提高测量速度。例如,1 kHz到100 MHz带宽的测量每次只需0.3秒。

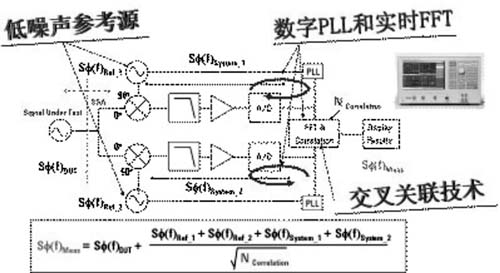

图7 Agilent E5052B信号源分析仪的先进体系结构

利用交叉关联技术获得出色的抖动本底噪声

E5052B抖动测量分辨率和本底噪声非常低,通常10Gbps速率时的RJ本底噪声仅为几飞秒。由于ADC的动态范围有限,且其内部参考时基的剩余抖动较大,高性能(实时或采样)示波器的抖动本底噪声通常在一百飞秒以上。E5052B通过检测基带(其中较大的载波信号已删除)的相位噪声来保持宽动态范围。E5052B利用两个独立的内部测量通道之间的独特交叉关联技术,将抖动测量极限扩大到低于其内部时基的残余抖动。(参见图7)与目前的高性能示波器相比,E5052B利用这种交叉关联技术把抖动本底噪声降低了100倍到1,000倍(图8)。

评论