利用频域时钟抖动分析加快设计验证过程(07-100)

—— 利用频域时钟抖动分析加快设计验证过程

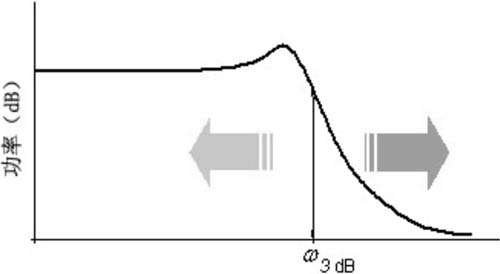

图3 PLL频率响应

真实的抖动源

如果观察实际环境中的高速数字电路,您会发现许多抖动源,如图4所示。跟我们前面讨论的一样,时钟信号通常分配给多个IC,时钟频率可能进行乘法和/或除法运算。假设来自晶体振荡器的参考时钟具有较低的抖动,因为IC带来的附加噪声或其他设备产生的干扰,所以经过乘法或除法运算的输出时钟也可能不是非常干净。

一个主要污染源就是开关电源的噪声。开关频率一般为100 kHz到1 MHz。开关电源噪声可能会注入时钟信号线路,它在左下图中显示为PJ。

其他周期抖动分量的来源可能是数据或时钟线路的干扰,经互调后可能位于时钟线上,也显示为PJ分量。只要PJ分量表现的远离时钟频率,它就极有可能插入带通滤波器(或低通滤波器)来消除这些抖动。然而,问题是周期抖动在什么时间接近时钟频率,因为高频高Q滤波器很难得到。参考时钟的RJ也一样,时钟除法器可能添加宽带噪声,这可能会使输出时钟信号的RJ增加。

要诊断各种问题,设计人员必须表征有关电路物理布局和/或工作环境下的时钟抖动。

评论