SERDES的FPGA实现(07-100)

—— SERDES的FPGA实现

抖动测量装置

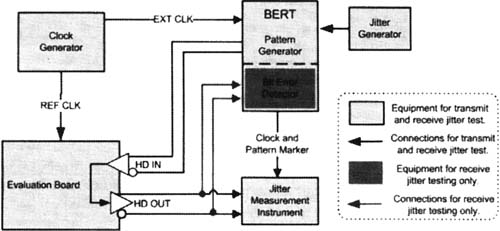

本文引用地址:http://www.eepw.com.cn/article/91924.htm为了检测发送抖动,由误码率测试器(GERT)产生测试图形,并送到评估板的SERDES接收端口。同样,时钟产生器连接到评估板的SERDES时钟。把FPGA配置为内部环回被测信道。这样,被接收的测试图形在TX引脚发送。示波器连接到TX SERDES连接器,这样可以分析发送抖动眼图。所有评估板SERDES连接都用50? SMA连接。图3示出这种配置。

用FPGA SERDES接收端口处的施感抖动和监控环回SERDES输出的误码,来测量接收抖动容限。连接抖动产生器到BERT图形产生器(见图3)。BERT产生器送一个伪随时机图形序列到评估板的SERDES SMA输入。这种配置可使工程师在控制状态下,引入抖动到SERDES RX端口。配置FPGA用于环回,SERDES TX端口连接BERT上的误码检测器端口,工程师引入抖动,并观察FPGA所产生的误码率(BER)。当BER超出技术要求时,就可知道已超出抖动容限阈值。对于FPGA,此数值就等于或大于特定的接收抖动容限。

图3 抖动测试设备配置

背板性能测量

通过一个背板配置驱动FPGA的TX信号,可以测量FPGA的SERDES链路发送特性,并可以分析背板输出的眼图。此装置首先用BERT图形产生器,把PRBS位流馈入FPGA评估板的SMA RX端口。用环回配置的TPGA,PRBS将呈现在评估板TX端口,并驱动馈入背板的同轴缆线。系统要求决定测试参量,如PRBS图形选择,背板和FPGA评估板线长、用轴缆线长度、预矫和均衡设置、工作温度和Vcc。

评论