用FPGA实现FIR滤波器(08-100)

——

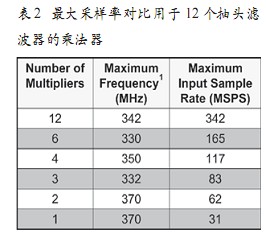

接下来要做的事是决定使用多少个乘法器。对于最快的速度,乘法器的数目等于FIR滤波器中抽头的数目。这种类型的滤波器完全用并行形式来实现。然而在许多情况下,并不需要性能的级别,允许乘法器时间共享。一种快速计算揭示了使用的乘法器的数目。首先做一个简化,以采样率除速度,你认为适中的复杂设计可以运行于所选的FPGA,然后对这个数进行四舍五入至最接近的整数。通过这个计算因子,可以减少乘法器的数目。作为一个例子,假设要在LatticeECP2 FPGA中实现12个抽头,75MSPS,12位的滤波器。用这个器件,300MHz的滤波器比较容易实现,减少因子为4,需要3个乘法器。

本文引用地址:http://www.eepw.com.cn/article/91694.htm在做出最后决定之前,要考虑最终的实现。例如,使用Lattice提供的FIR产生器,这个工具用sysDSP块内的加法树实现FIR滤波器。因为这个加法树的范围是4个乘法器,没有有效的资源与指定的3个乘法器联系在一起。此外,如果指定了4个乘法器,设计要求的工作速度会略有降低。

表2 最大采样率对比用于12个抽头滤波器的乘法器

现在有了系数,乘法器实现的方法,以及知道需要多少个乘法器。许多供应商,包括Lattice提供自动产生FIR的工具。最后一步是把系数输入工具,指定乘法器的数目。产生滤波器之后要进行时序分析,确定是否假设的速度是正确的。在使用的例子中,工具报告了350MHz的最大速度,高于假设的300MHz。如果速度非常接近,你应该进行调整并再试。

评论