3G中的CMOS基RF集成(05-100)

CMOS优点

本文引用地址:http://www.eepw.com.cn/article/91467.htm用CMOS技术实现收发器有下列优点:

- CMOS与SiGe BiCMOS工艺相比,在相等的工艺尺寸具有更低晶片成本结构。

- CMOS允许用标准工艺在多个厂家进行芯片制造。

- 根据Moore定律,CMOS设计可以定标更小工艺尺寸。

- CMOS能够实现RF功能数字电路,导致高度可编程设计,使其具有小的芯片、高度可制造性,良好的坚固性。

- CMOS收发器可以集成其他功能(如DigRF接口或数字基带功能),从而构成单片RF和基带元件。

- CMOS已证明是实现收发器的一种技术,厂家已生产出大量GSM/GPRS、WLAN和蓝牙无线电。

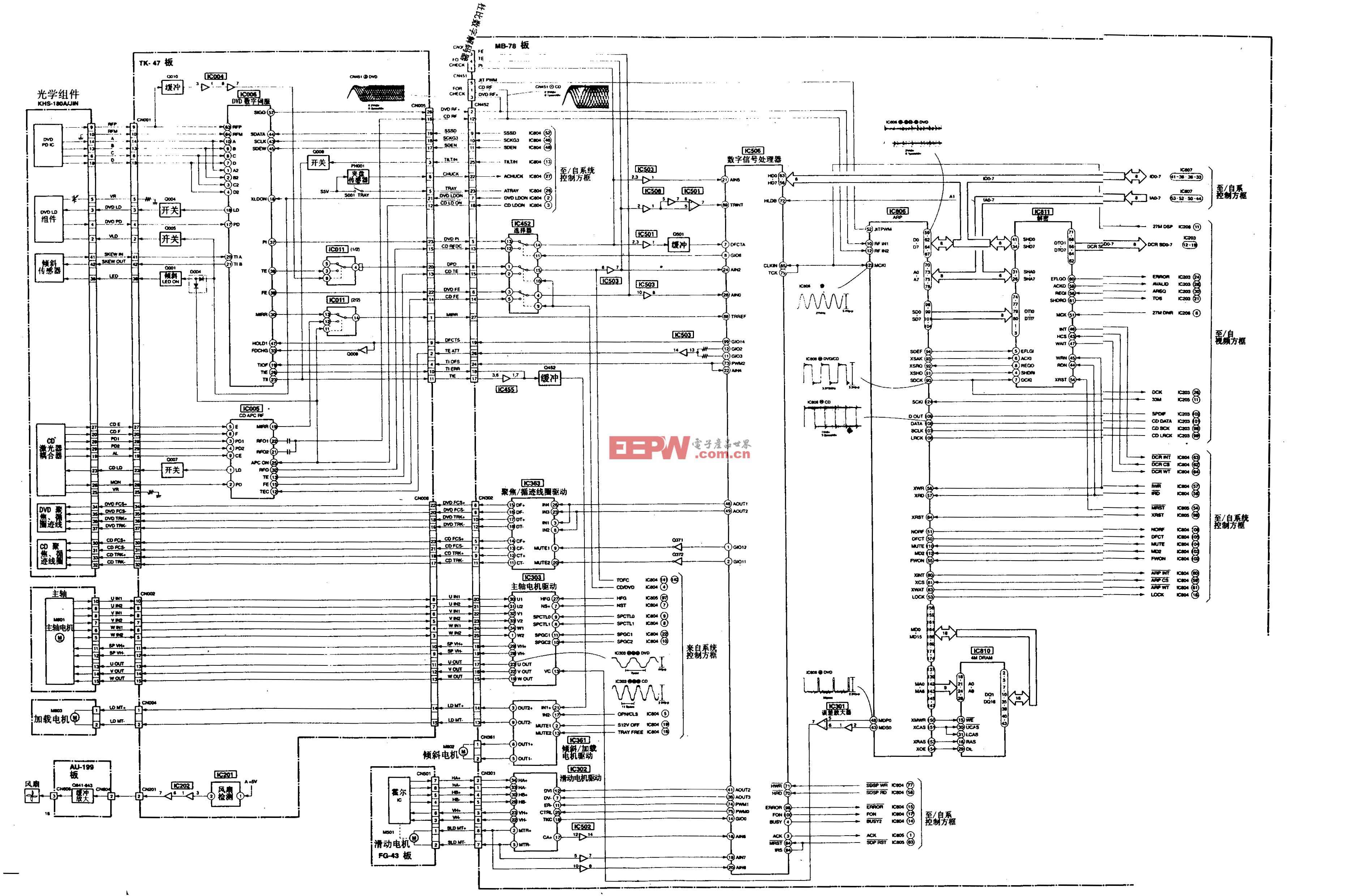

多模GSM/GPRS/EDGE/WCDMA手机选用收发器结构,是一个关键决定。现在,在很多单片CMOS GSM/GPRS收发器中,通常集成VCO、频率合成器、环路滤波器和DCXO,这种集成特别重要。高集成有助于保证良好的无线性能,这是因为关键功能与外部噪声源屏蔽。

在恒定幅度的GSM/GPRS 阻断器和调幅EDGE或WCDMA阻断器中的接收器,必须提供良好的幅度调制抑制功能。与传统超外差设计相比,最流行的接收器结构是低中频或零中频,其中所设计的接收器和发送器链路不需要外部IF SAW滤波器。

直接变频接收器,直接变换输入信号为低频信号,便于实现可编程滤波器。直接变频无线电的一个问题是由大阻断器的本地振荡器自混频引起DC偏移出现,因而恶化下变频信号。解决此问题往往需要基带执行DC偏移校正,通常是通过软件来实现。在低中频接收器中,通过混频和滤波从所希望的下变频信号中去掉DC偏移。此外,低中频设计通常具有集成合成器、环路滤波器和调谐元件来防止外部相位噪声源引起的相互混频。

对于发送器,线性上变频结构往往最适合于GSM/GPRS、EDGE、CDMA和WCDMA,而极性环路设计主要用于EDGE收发器。线性上变频结构在贯穿发送器链路中(从其带I和Q信号到天线)保持线性。基于极性环路或极性调制的无线电靠牺牲附加定标和所需功率控制反馈环路复杂性来提供附加的高功率效率。此外,极性发送器需要一个特殊定制的PA,来保证幅度精确匹配和相位延迟。线性发送器不像极性发送器那样,它可以广泛地采用现有PA元件。

单片4频段GSM/GPRS设计

为了成功地开发一款支持3G和2G服务多模CMOS无线电,收发器IC公司在力图用其他模式组合(如EDGE和WCDMA)设计器件前,必须证明它有能力为GSM/GPRS应用开发和制造单片多频段CMOS收发器。

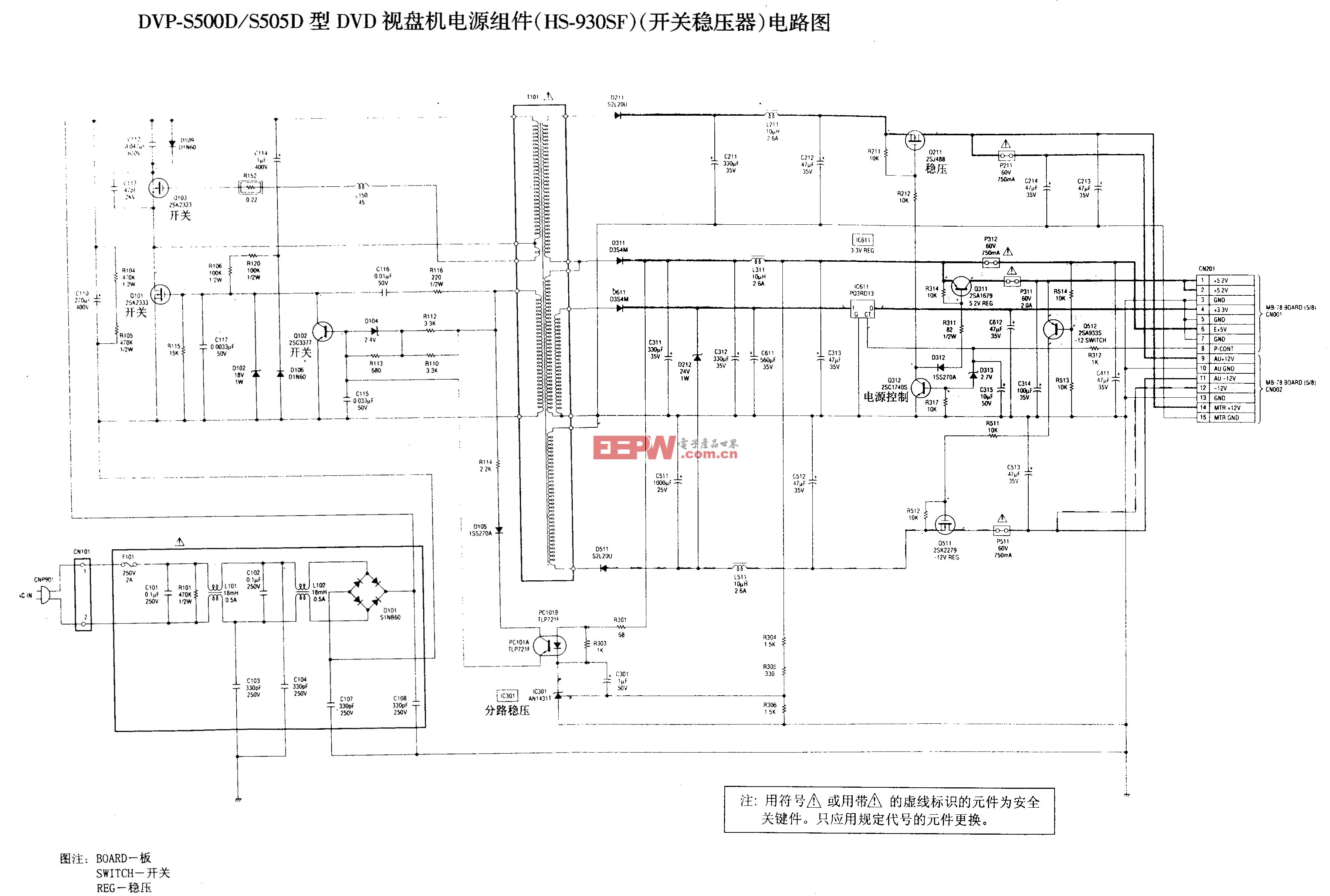

图4示出一个4频段GSM/GPRS CMOS收发器设计。4频段接收器用低中频结构代替零中频,因低中频受1/f噪声、DC偏移和有限接收器IIP2的影响较小。用片上电感负反馈的全差分共源放大器实现LNA,用于阻抗匹配和增益峰值。LNA也执行低增益模式。

LNA之后,正交混频器下变频所希望的RF为低中频。接收器的低中频部分由5阶复杂Butterworth滤波器和PGA组成。每个复杂滤波器级为GSM阻断器和图像信号提供抑制,并提供所希望信号的可编程放大。增益分布和滤波器极的定序使总Rx SNR最大。可编程增益IF滤波器与LNA增益结合在一起具100dB可编程增益。DCOC电路防止IF增益级饱和。滤波器I和Q通道之间电阻交叉耦合导致I信道上DC偏移影响Q信道,反之亦然。复杂滤波器之后,低中频解调电路下变频IF I和Q信号为基带频率(用数字合成时钟)。

发送器结构是基于OPLL基础上的,它包括一个正交调制器和一个完全集成的低相位噪声RF VCO。由正交调制器把基带I和Q GMSK信号变为IF。一个5阶Gm-C低通滤波器可消除不希望的频率分量。用片上环路滤波器滤波PFD输出,此输出用于驱动RF VCO ,RF VCO含盖GSM-850、GSM-900、DCS-1800和PCS-1900频段。

VCO输出驱动片上发送缓冲器。此缓冲器的RF输出电平可编程到适应不同的PA模块。单端输出不需要外部平衡—不平衡转换器。片上VCO相位噪声和TX前置PA驱动器噪声一起决定接收频段的TX输出噪声(这是GSM发送器的最严格性能指标之一)。为使噪音减小、DC电流耗电减少,从VCO输出到前置PA驱动器,输入保持在轨到轨信号或后置PA发送带通滤波器,因此,改善了发送器功率效率。

用单频率合成器为发送器和接收器产生本地振荡信号,以此利用GSM的时分双工特性。用3阶△ΣN分合成器来为Tx和Rx模式频率设计提供最大灵活性。用带片上电感器的VCO,来满足Rx和Tx相位噪声所要求的容限。

结语

扩大数字领域的设计复杂性,发挥高密度CMOS逻辑的有效性。实现良好的结构(包含延伸的DSP技术和共用功能单元),是成功和经济设计的最基本要素。

靠解决实现单片4波段GSM/GPRS CMOS收发器问题,RF集成电路设计师可以解决支持EDGE、WCDMA和其他无线技术的单片无线电开发问题。把高集成前端模块和数字接口基带IC结合在一起,所得到的CMOS收发器可以实现经济、小形状因数多模手机。■(林)

评论