应用于汽车和航太电子显示产品中的双线介面

成果

本文引用地址:http://www.eepw.com.cn/article/85783.htm为了面对这些严苛的要求,美国国家半导体开发出一款能够有效解决这些技术挑战的LVDS SERDES(串列解串器)晶片组DS90C2411 和DS90C1241。

SERDES的特点

这款晶片组将接收高达24位元的并行CMOS/TTL电位资料,以及来自图形或视频资料源资料相关的时脉源。资料和时脉将在单个差动对上串列传送。24位元资料可以被用来表示显示颜色资料(共18位元或6位/颜色)和控制讯号(Hsync, Vsync和资料使能)。对于最大840Mbps的合成频宽,能支援从5MHz到35MHz的频率(今后可以扩展到65MHz)。

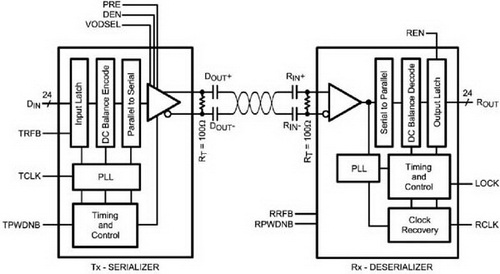

透过介面上的资料源和接收器两侧的差动对的每个脚/电源上分别加入电容(参见图1),能够有效地实现介面连结的交流耦合。电容将有效地阻挡连结上任何直流电位的偏置,这样就成功的隔离接收器与资料源以及它们与自身的电源。通过这些相同的电容实现的任何直流电位的隔离,实际上只让更高频率(大于1MHz)的交换内容通过电实体介面连结。在此情况下,串列化讯号本身实际上是在与LVDS电气电位(+/- 350 mV)类似的差动电位上进行交换的。与其他类型的介面相比,这一较低的差动摆幅电位会带来相对更低的功耗和EMI效能。

图1:双线串列介面

数量减少的互连

在这款新产品中采用了两种方法,大幅度减少了互连的数量:

·嵌入式时脉

·较宽/大的串列比

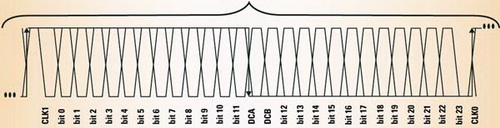

高达24位元的并行资料和时脉输入串列器(DS90C241)。串列器将并行资料转换成串列化资料(24:1),使其能够通过低成本的铜互连线构成的差动对(双线)进行发送。除并行资料外,时脉(CLK1和CLK0)和其他维持直流平衡和连结完整性(DCB和DCA)所必须的附加位元也与实际的资料位元一起被串列化(参见图2)。将时脉嵌入到资料中,能消除当资料和时脉在解串器一侧被恢复时,可能会产生和引起资料错误的时脉到资料边沿歪斜问题,并从中获得关键性的好处。

随机数据锁定和热插拔

此款产品的另一个独特之处,在于不像其他的介面解决方案那样必须在解串器一侧使用一个参考时脉,来对嵌入式时脉讯号进行识别和/或解码。其解串架构具有一项独特的优点,那就是无需在解串器中使用任何参考时脉,就能锁定所有随机数据模式(RDL,随机数据锁定)。RDL特点为实现另一项终端用户的优势“热插拔”创造了条件。“热插拔”的特点能够促使解串器重新锁定到电缆连接和断开时可能出现的断开后有效、断开无效和断开的串列化资料流程。在此情况下,不需要任何特殊的时脉训练模式或介面连结的特殊初始化序列,介面就能容易地重新锁定。

交流耦合和直流平衡

由于整个介面连结是交流耦合的,因此介面连结必然很容易受到引起1或0非平衡密度的直流电荷的影响。连续的1或0会在连结上建立潜在的直流电位电荷,这会妨碍一个状态(1或0)到另一个状态的正确转换,从而导致出现资料错误。这一种效应也被称作ISI,符号间干扰2。因此,为了降低ISI效应,国家半导体新的介面产品中采用了一种整合的直流平衡演算法。

长距电缆驱动

为了能够在10公尺的电缆驱动长度下,得到高达1Gbps(或840Mbps)的频宽,必须在电缆的末端得到干净并且较大的“眼图张开度”(“Eye” openings),以确保接收解串器能可靠地恢复资料。过量的抖动和电缆引起的讯号损失 2等因素都会阻止“眼睛”张得更大。通过对串列器中的PLL(锁相环)进行精确的设计能减小或消除过量的抖动。为了克服由电缆负载所引起的讯号损失,因此采用了一项被称为预放大2的技术,其本质上是在串列化资料流程的开关转换处对讯号进行过驱动/提升处理。

图2:串列化配置和协定

结论

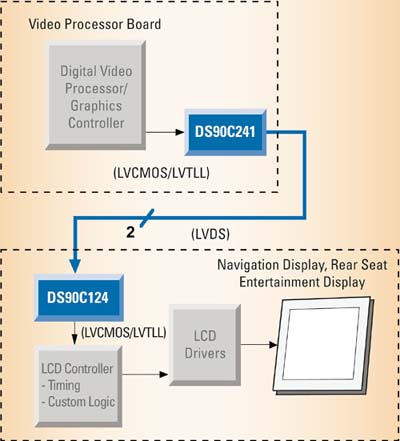

透过美国国家半导体新型显示SERDES产品DS90C241 / DS90C124 SERDES的介绍,图3展示了一款的新型数位显示介面,它适用于要求特别严格和/或苛刻的远距离应用,并在SVGA(800x 600)/42 MHz解析度下的工作距离长达10公尺。该介面架构能容易地升级到更高的频宽,用来支援未来如XGA或更高的显示解析度。

图3:典型应用-后座资讯娱乐与导航显示

评论