片上系统(SOC)设计流程及其集成开发环境

那么,从板级电子系统设计到芯片级电子系统设计转变将导致哪些方面的变化?主要表现在如下几个方面:

本文引用地址:http://www.eepw.com.cn/article/85492.htm(1)在设计描述工具方面,传统的板级电子系统设计主要采用电路原理图和元器件外形封装图作为设计描述语言工具,而现在的芯片级电子系统设计主要采用文本方式的硬件描述语言(HDL——Hardware Description Language)作为设计描述语言工具;

(2) 在设计流程方面,板极电子系统设计主要经历电子系统原理图设计与仿真、印刷电路板(PCB)设计与仿真分板(包括信号完整性分析、电磁兼容性分析等)等二个阶段,而芯片级电子系统设计通常需要经历系统级设计与仿真、算法级设计与仿真、寄存器传输级(RTL)设计与仿真、逻辑综合与验证、版图设计综合与验证等5个阶段;

(3)在软硬件协同设计方面,板级电子系统设计所采用的方法是先进行硬件系统设计后再进行软件系统设计的方法,难以实现软硬同步设计或协同设计,而芯片级电子系统设计可以比较容易实现软硬件同时设计或协同设计;

(4)在设计实现方面,板级电子系统设计主要基于具有特定功能的集成电路器件,而芯片级电子系统设计主要是基于具有特定功能的电路模块——知识产权核(IP核)。因此,板级电子系统设计与芯片级电子系统设计无论是在设计方法上还是在设计工具方面都发生了较大的变化。

随着现代信息技术的发展,电子产品生命周期越来越短,特别是电子工业技术不断发展,基于深亚微米和超深亚微米的超大规模集成电路技术的片上系统(SOC) 芯片需求日益扩大,传统的板级电子系统设计方法已不能适应产业界对电子产品需求。因此,基于知识产权(IP)核复用的芯片级电子系统设计方法将成为嵌入式系统设计的主流方式。

2 基于可编程片上系统(SoPC)的设计流程

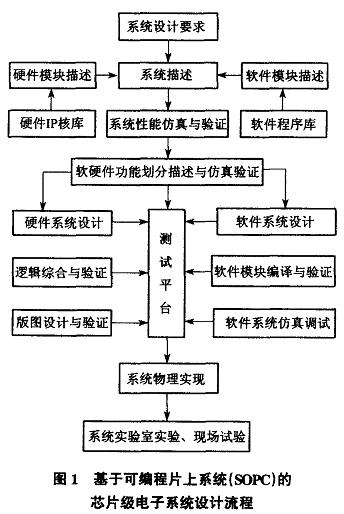

基于可编程片上系统(SOPC)的芯片级电子系统设计主要有两大支撑点:可编程片上系统器件所能提供的片上资源和可复用IP核库所能提供的IP核资源。其中,可编程片上系统器件所能提供的片上资源是由集成电路工艺技术发展决定的,对于系统设计者来讲,应根据设计要求尽量选择合适的器件;可复用TP核库所能提供的IP核资源需要通过系统设计者自行建设。在基于SOC的电子系统设计中,针对各类专门技术、专门应用、专门工具、专门生产工艺、专门产品的IP资源库的建设和共享已形成一种规范,贯穿在系统设计的全过程。图1为典型的基于IP核库的片上系统(SOC)设计流程。

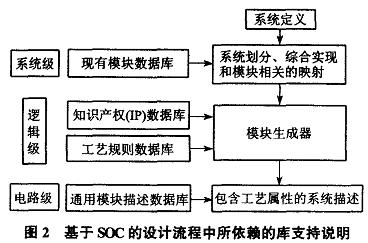

从图1可以看出,在基于可编程上系统(SOPC)的嵌入式系统设计流程中,除了需要强有力的EDA设计工具支持外,离开充分的资源库的支持,可以说是寸步难行,并且必将失去竞争力。从总体上讲,各个层次的IP库和EDA工具是芯片级电子系统设计者必备的两翼,可选的IP核库资源是一种设计者能力的表征。图 2为芯片级电子系统设计中自顶向下设计方法的流程中所依赖的库支持说明。

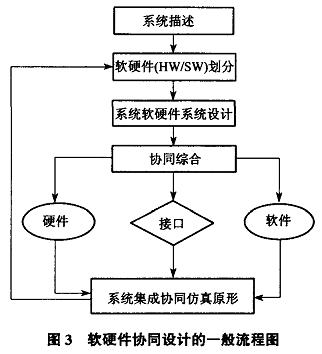

在图1的片上系统(SOC)设计流程中,除了需要强有力的IP核库和EDA工具支持外,与传统的专用集成电路(ASIC)设计流程最明显的区别就是——软硬件协同设计,图3给出软硬件协同设计的一般流程。在软硬件协同设计的过程中,传统的硬件描述语言(VHDL、Verilog HDL)和软件设计语言(C/C++)是无法适应软硬件协同设计这一种新的设计方法上的突破,为此必须使用新的系统级描述语言——System C(或其他类似语言)才能完成。

软硬件协同设计通常是从一个给定的系统任务开始的,通过有效地分析系统任务和所需要的资源,采用一系列的变换方法并且遵循特定的准则,自动生成符合系统功能要求的、符合实现代价约束的硬件和软件框架。这种全新的软硬件协同设计思想需要解决许多问题:系统级建模、系统级描述语言、软硬件划分、性能评估、协调综合、协同仿真和协同 验证。

评论