半导体集成电路的发展及封装工艺面临的挑战

5 焊线工艺中焊线区金属层与ILD层的剥离

本文引用地址:http://www.eepw.com.cn/article/84972.htm由于低k材料质地相对较软,在焊线过程中,由焊线机对焊线垫(Bonding Pad)施加的压力和超声波能量会使焊线垫及其下方金属/ILD层产生杯状变形(Cupping Deformation)(图5),这种杯状变形减弱了超声波能量到焊线区的有效传输,从而阻止了金铝两种原子的相互扩散,导致断焊(Non Stick),或弱焊(Weak Bond)。当有意识地增大超声波能量来弥补因杯状变形造成的超声波能量损失时,又会因为ILD层与金属层较弱的粘接力及低k 材料的脆性而产生焊线区下方金属层与ILD层的剥离[8]。

初始的低k芯片的焊线评估显示,低k芯片对焊线程序参数(焊线能量- Bonding Power,焊线力- Bondinge)十分敏感,较小的焊线参数设置会导致断焊或弱焊,而较大的焊线参数设置又会容易产生金属-ILD层的剥离(图6)。而焊线区尺寸(BPO- Bond Pad Opening)及焊线区间距(BPP Bond Pad Pitch)的不断缩小使得焊线工艺窗口变得更窄。对于 65nm技术的芯片设计,其焊线区宽度只有40um,使得低k焊线垫的结构及焊线垫下方的低k材料对焊线质量和可靠性的影响更加显著。这些问题要求对低k 材料的焊线工艺进行进一步的开发和优化,以提高其可制造性和可靠性[9-11]。

图6焊线过程中的NonStick和金属层与ILD层的剥离

6 封装工艺对低k产品可靠性的影响

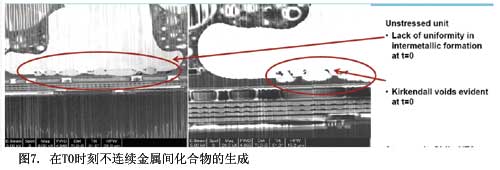

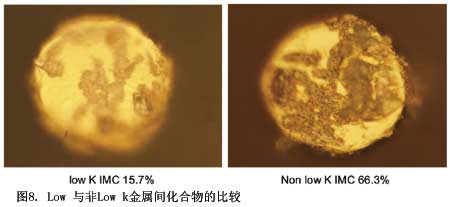

实验与数据证明,金铝焊线界面的完整性(Integrity)在长时间的温度应力作用下会逐渐下降,直至电性开路[10]。这种失效主要是由于金-铝间化合物(IMC Intermetallic Compound)随时间历程其化和物相态逐渐发生改变,最终形成Kirkendall 空洞并出现IMC分层而造成的。在研究中发现,金属间化合物的这种失效模式与其初始的焊线状况有很大联系,比如不连续的T0 IMC(如图7所示)。初始焊线状况包括焊线垫及其下方的材料和结构,焊线垫表面的清洁状况,使用的焊线材料及工具以及焊线参数等.而当低k铜工艺技术与细间距焊线(Fine Pitch Wire Bonding)相结合时,金铝金属间化合物对封装的可靠性的影响就更大了。对细间距焊线而言,变形后的焊球尺寸不能很大,因而形成的IMC的面积也受到了制约。在如此小面积的焊线区中,由于厚的氧化铝薄膜或前道工序在焊线区表面遗留的化学污染都会造成焊线区域的局部非润湿(Non Wetting),又因为超声波能量受低k材料影响而不能有效传输,所有这一切都会阻碍金铝金属间化合物的充分形成。一个观察到的现象是低k材料芯片的金属间化合物占变形金球面积的比例要小于非低k材料焊线形成的金属间化合物(图8)。这也就意味着低k材料的焊线具有更 多的初始空洞/非润湿区域。当焊线区内含有针测的印迹(Probe Mark)时,这种现象就更加明显。在随后的可靠性测试中,含有空洞的表面提供了一个供金属间化合物扩散的途径,结果是空洞尺寸沿空洞界面不断增大,最终会导致金属间化合物的分层(图9),电路不再导通,电性失效。

图7在T0时刻不连续金属间化合物的生成

图8Low与非Lowk金属间化合物的比较

图9经过504小时高温存储测试后金属间化合物的分层

总结

半导体芯片结构尺寸的缩小使得RC延迟成为制约集成电路性能进一步提高的关键性因素。转向低k铜工艺技术是业界给出的解决方案。双大马士革工艺取代了传统的铝“减”工艺,成为低k铜互连材料的标准制造工艺。

为了能与芯片制造工艺完美结合,不产生可靠性问题,低k绝缘材料必须具备一系列期望的材料特性,对低k材料研发本身的挑战在于:在获得所需要的低介电常数的同时,低k材料还必须满足良好的热和机械特性。但目前并没有完全符合这些期望特性的低k材料被制造出来,因而给半导体制造工艺带来了挑战。

由于低k材料本身的材料特性(与金属层较弱的粘结力,较弱的机械强度),晶片切割时在芯片的边缘会出现严重的金属层与ILD层的分层或剥离;在焊线过程中会出现断焊,弱焊或金属层与ILD层的剥离。金铝两种材料的焊接在可靠性测试中出现比非低k材料焊线严重的金属间化合物的分层,导致集成电路电性失效。上述这些可制造性及可靠性的问题构成了对半导体封装工艺的挑战。

万能遥控器相关文章:万能遥控器代码

电路相关文章:电路分析基础

pic相关文章:pic是什么

评论