FSL总线IP核及其在MicoBlaze系统中的应用

4 FSL总线应用实例

在下面的实例中,尝试通过FSL总线技术,将实现特定函数功能的用户自定义IP核整合到MicroBlaze软核系统中,以实现硬件加速的目的。这里以一个矢量汉字(vector font)还原功能的硬件模块的整合为例,说明FSL总线的应用过程。所使用的开发平台是Memec Insight公司生产的Virtex—II系列的MicroBlaze开发板,板上采用的FPGA器件为Virtex—II 1000,系统时钟为100 MHz,开发工具为Xilinx公司的EDK 6.3及ISE 6.3。

4.1 FSL总线应用方案

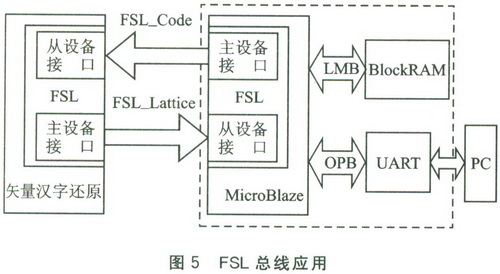

如图5所示,vectOr_font核通过FSL_Code-与FSL_Lattice两条FSL总线与MicroBlaze软核直接相连。

对于FSL_Code总线,MicroBlaze核是主设备,而vector_font核是从设备。这样MicroBlaze可以通过 FSL_Code总线向vectOr_font核发送汉字的区位码(或者其他格式的汉字编码,由使用的矢量字库和还原算法决定)以及汉字的属性信息(如字体、大小等)。

对于FSL_Lattice总线则正好相反。vector font 核作为主设备可以通过它向MicroBlaze核发送经过还原处理后的汉字点阵数据以及汉字点阵尺寸信息(用于将点阵数据在显存中组织成正确的显示格式)。

4.2 数据传输指令与控制位指令的应用

FSL 提供的独立于数据传输的控制位可以用来对正在传输中的数据进行标记。为了区分区位码数据与汉字属性数据,以及点阵数据与汉字点阵尺寸数据。 MicroBlaze分别通过FSL的数据传输指令和控制位传输指令来发送汉字的区位码和汉字属性信息,接收点阵数据和汉字点阵尺寸信息。对应的实现代码如下:

//使用非阻塞的数据写函数向FSL总线写入汉字区位码Microblaze_nbwrite_datatsl(code,O)

//使用非阻塞的控制位写函数向FSL总线写入汉字属性信息maicroblaze_cnbwrite_cnlfsl(attibute,O)

//使用非阻塞的数据读函数从FSL总线读取汉字点阵数据microblaze_nbread_datafsl(1attice[i],O)

//使用非阻塞的控制位读函数从FSL总线读取汉字点阵尺寸信息microblaze_cnbread_cnlfsl(size,O)

代码中用到的与FSL有关函数的定义,都在include目录下的mb_inteRFace.h文件中。其中,各函数的第二个参数代表进行读写操作的 FSL总线接口的编号,对应Mi—croBlaze软核的8对FSL接口。该参数的取值范围从0到7。本例中,MicroBlaze只使用了一对FSL接口,故而值为0。

4.3 实现步骤

首先,在Base System Wizard中设计图5虚线框中所示的一个简单的MicroBlaze嵌入式处理器系统。然后,在XPS集成开发环境下完成用户自定义IP核(本例中即 vectoz__font核)的添加、Microblaze核FSL接口的添加(设置参数C_FSL_LINKS=1),同时添加两个FSL总线IP核,分别用于实现FSL_Code和FSL_Lattice总线。另外,将两个FSL总线IP核的参数C_USE_CONTROL置为1,以打开FSL总线的控制位传输功能。所有这些改动,最后都会被更新到MES文件中。这样,硬件平台生成工具platgen就可以根据它生成所需要的FPGA配置文件了。

硬件的实现完成后,进行相应软件参数的设置,如将系统标准输入输出设备指向UART模块等。然后,用库生成工具libgen,根据MSS(系统软件描述文件)文件,将所需外设函数库的头文件添加进工程中。

通过调用这些函数,可以操作和控制这些外设。通过Tool项里的build命令,调用mb—gcc:编译工具,将编写的应用程序编译成ELF文件,再用 updatebitstrcam命令将程序代码对应的RAM初始化数据添加到前面生成的FPGA配置文件中,生成最终的bit配置文件。最后,使用 download命令将bit文件下载到目标板中。

以上就是整个FSL应用实例设计的实现过程。本例只是为了说明FSL总线的使用。实际应用中,还可以根据具体情况通过FSL,将更多的用户自定义IP核(如DCT、FFT等)添加到.MicroBlaze软核系统中去。

结 语

在嵌入式系统的开发中,人们一直希望能够有一个满足自己需要的“定制”的嵌入式处理器,而不是手头大量存在的通用微处理器。但是,直接将用户自定义IP 核添加到处理器核中,不仅受到处理器原架构的束缚,还有可能降低处理器的性能(处理器工作频率);而通过与内部寄存器直接相连的FSL接口,用户自定义 IP可以在不破坏处理器原有结构的情况下,紧密地与MicroB- laze软核结合在一起。这样,即使关键路径覆盖了用户IP 核,由于它在处理器内核之外,也不会导致处理器时钟频率的降低。

通过对FSL总线的分析以及上述实例的验证,证明了在基于 MicroBlaze的SoC 系统设计中,一方面可以针对具体应用进行“量体裁衣”式的设计;另一方面,利用其专用的FSL总线接口技术,实现嵌入式软处理器系统与用户自定义逻辑的整合,从而在不提高系统主频的前提下,通过部分函数功能的硬件实现来提升系统的性能。

评论