一种ARM+DSP协作架构的FPGA验证实现

介绍了以ARM+DSP体系结构为基础的FPGA实现。在其上验证应用算法,实现了由ARM负责对整个程序的控制,由DSP负责对整个程序的计算,最大程度地同时发挥了ARM和DSP的各自优势。

本文引用地址:http://www.eepw.com.cn/article/83026.htmARM通用CPU及其开发平台,是近年来较为流行的开发平台之一,而由ARM+DSP的双核体系结构,更有其独特的功能特点:由ARM完成整个体系的控制和流程操作,由DSP完成具体的算法和计算处理。这样,不但可以充分地发挥ARM方便的控制优势,同时又能最大限度地发挥DSP的计算功能。这在业界已逐渐成为一种趋势。

本文的FPGA的Demo验证,是在基于一款DSP内核处理器的研发基础上,对其功能进行验证的一个小目标识别算法的实现。考虑到软件环境仿真的速度以及仿真模型的局限性,用FPGA进行硬件协同验证。这样,既能够保证仿真的真实性,又能够快速发现实际问题,减少不必要的流片次数,加快开发的进程,这对于一个大规模的SoC设计,已经成为不可或缺的手段之一,而且对节约成本也有很大好处。

1 系统体系结构

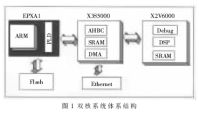

双核系统的体系结构如图1所示。

1.1 内嵌ARM内核的EPXA1芯片及其特点

图1中,包含ARM922T内核的开发平台选用的是Altera公司的excalibar系列,本验证实现选用的型号是EPXA1。EPXA1是一款带有100万门可重配置PLD的ARM Core+PLD体系结构,可以通过quartus II软件工具来灵活配置ARM Core同外部的端口连接,最大时钟频率能够达到200MHz。EPXA1的高度集成化,不仅大大加快了ARM与片内各种资源的通讯速度,而且减小了硬件电路的复杂性、体积和功耗,真正实现了SOPC[1]。

1.2 FPGA硬件平台及其特点

对于一个具体项目,FPGA芯片的选取要根据实际需求和特点来具体考虑。一般应从逻辑资源需求、易扩展能力、信号质量以及成本等因素来考虑。如图1所示,本次设计采用的两片FPGA分别为Xilinx公司的FPGA X3S5000和X2V6000,其容量分别为500万门和600万门。选用这两块芯片正是基于逻辑资源需求的考虑。FPGA X2V6000面向高端应用,存储资源更多,功能更强大,适用于性能要求较高的DSP内核,但其成本相对也较高;而FPGA X3S5000成本较低,适用于一般性能要求的模块。两片FPGA都具备三个扩展槽,可做接口扩展,同时也能作为调试测试点用。

1.3 双核体系结构设计特点

具体来讲,整个体系结构是指通过人为设计电路图,外部选用不同的FPGA器件来下载生成特定功能的外部硬件电路,在电路图上对应相应的端口标号;同时,ARM Core可以通过quartus II工具方便地连接不同的端口标号,编译运行生成相应的配置文件;ARM的启动代码中用以上的的配置文件信息来配置PLD,从而实现ARM同外部硬件电路即两片FPGA的连接[3]。FPGA X3S5000中下载固化AHBC硬件电路以及外部SRAM Memory,而FPGA X2V6000中下载固化DSP Core以及支持AMBA协议的Wrapper。

这种体系结构能够充分利用硬件资源,合理的版图位置方便了ARM和DSP对外部SRAM的访问,同时可快捷地实现ARM的控制功能,而且预留的扩展槽能够较为方便地进行功能扩展和调试。DSP Core的Wrapper能够快速响应ARM的控制请求,调动DSP Core进入不同的工作状态。

2 系统工作流程及特点

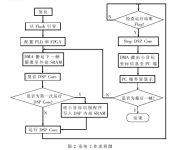

系统工作流程图如图2所示,介绍如下。

评论