微处理器和JTAG总线桥接接口(06-100)

——

到JTAG的并行接口

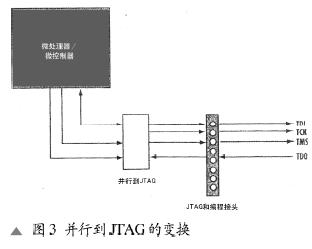

本文引用地址:http://www.eepw.com.cn/article/81431.htm微处理接入到JTAG链路的一种方法是采用并行总线到JTAG串行总线接口器件。这种器件提供一组寄存器,这些寄存器与微处理之间以并存方式传输数据。逻辑变换并行接入为串行JTAG协议。现在微处理器具有一种与板上JTAG逻辑相互连系的手段。

图3示出可以连接到基本JTAG链路的并行到JTAG的变换。此方案也必须具有断开JTAG输出的能力。若输出不断开(即处于三态),则用外接测试设备是不可能的。

此方案用一个外部变换替代控制器的端口I/O能力。设计人员必须权衡用固件控制执行,此功能比直接寻址外部变换逻辑所需的总线开销要少。

桥接在一起

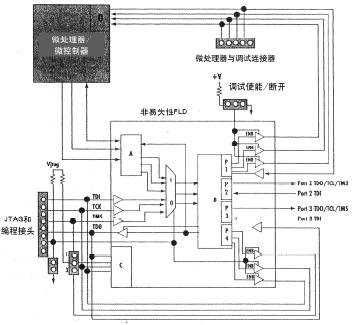

测试系统可分为两部分:端口链路器和并行到JTAG变换器。假定用分立可编程逻辑器件实现这两部分逻辑,则必须解决如何编程这些器件的问题。这些器件的每个部分都需要另外的专门JTAG接头或复杂开关系统的某种形式来控制TMS或TCK线。

替代这些功能于两个较小PLD器件的方法是把此逻辑置到一个较大的PLD器件中。图4示出如何把整个设计在单个PLD中。

评论