时钟技术的未来发展:向分组网络转型(06-100)

现在,我们向时钟卡移植混合型 PLL,比前代 TDM PLL 支持更多同步选择。混合型 PLL 可支持新的输入频率以及多达 5 种时钟参考选择:

本文引用地址:http://www.eepw.com.cn/article/81182.htm·传统 SSU/BITS 输入继续提供 1.544 MHz 或 2.048 MHz 时钟参考;

·系统中各种线路卡提取时钟。如果线路卡接口于 TDM 网络,则可能提供 8 kHz 的参考频率。如果线路卡接口于分组网络(如接口于以太网),则仍能提供 8 kHz 参考频率,即 25 MHz 除以 3125;

·冗余时钟卡提供的系统时钟用作参考,以便为系统提供相位对准的、频率锁定的冗余时钟;

·如时钟卡上有同步以太网接口,快速以太网 (FE) 或千兆以太网 (GE) PHY可为混合型 PLL 提供提取的 25 MHz 或 125 MHz 时钟参考;

·此外,如时钟卡上有以太网或 IP 接口,则时钟卡能支持RTP、IEEE 1588 或 NTP 等分组时钟 (ToP) 技术。图 1 所示的 ToP 器件可接收以太网或 IP 分组信息,并执行自适应时钟恢复工作,从而为混合型 PLL 提供参考源。

一旦混合型 PLL 选择了参考源,则不仅能够提供频率 为8 kHz、1.544 MHz 和 2.048 MHz 的 TDM 时钟,而且还能提供 25 MHz 和 125 MHz 以太网时钟频率。

作为一种可选项,混合型 PLL 还可内置 ToP引擎。在此情况下,混合型 PLL 能够支持时钟接口、合成时钟接口及分组接口。

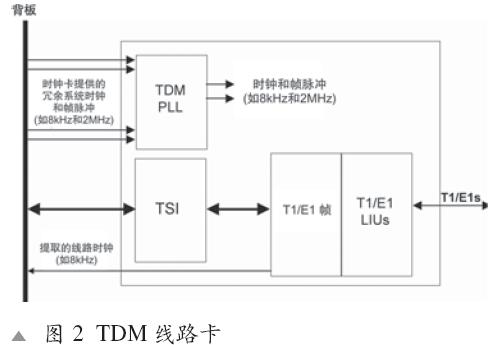

TDM 线路卡

图2 显示了当前 TDM 设备所用的简化型线路卡,可支持电路交换网络。出于简化目的,我们不妨假定该线路卡是通过 T1/E1 线路提供 NxDS0 语音服务。线路卡上的 PLL 可以是数字 PLL、模拟 PLL 或者数字与模拟 PLL。

评论