基于嵌入式TCP/IP软件体系结构的优化设计与实现(06-100)

——

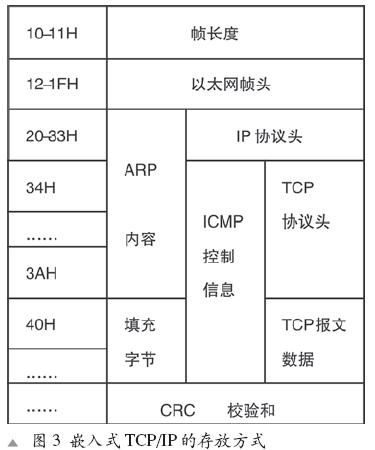

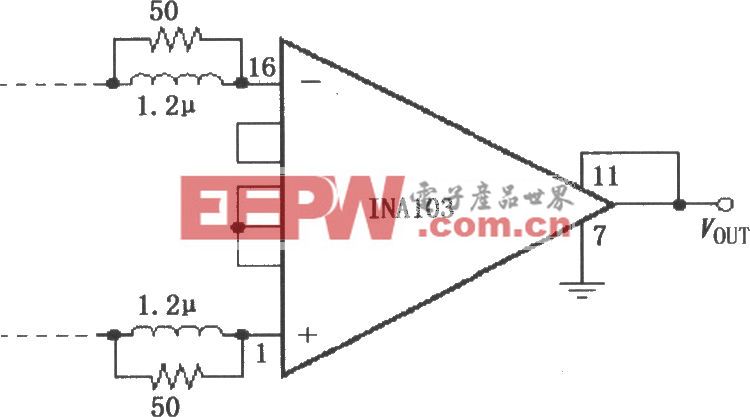

为了减小RAM使用量,当数据包需要重新发送时,如果能够重新产生数据包所需的数据,可以不存储需要被应答的TCP包。图3给出了嵌入式CPU中TCP/IP的内存划分,以及内存中帧的各个字节的定义和相对位置,其中PacketRAM为存放帧的首地址。

发送TCP/IP过程中主要的运算量集中在三个部分:应用程序将数据拷贝到RAM、计算TCP校验和、将RAM中的数据包拷贝到网络设备的发送缓冲区。对每一个字节数据,两次拷贝大致共使用12×2=24个指令周期;计算TCP校验和使用为16个指令周期。为提高速度可采用快速CPU或提高晶振频率。例如采用12M晶振时,网络传输速度为25K字节/s;而在高频PCB电路板使用233M晶振时,网络传输速度能达到为384K字节/s。

tcp/ip相关文章:tcp/ip是什么

评论