采用FPGA协处理器优化汽车信息娱乐和信息通信系统(04-100)

由主处理器控制专用硬件加速器,一般通过寄存器和存储接口实现,每个寄存器控制部分硬件加速器的运行。这适用于Delphi系统的默认协同芯片,也适用于下载到协同FPGA中的协处理器体系。通过使用FPGA可以直接将寄存器和存储器接口标准化,以控制任何编程实现的协处理器。标准化的接口可以定义怎样读取和写入协处理器数据,怎样开始和停止这一过程,怎样进行复位,并包括了一组寄存器实现控制专用操作。所有这些寄存器都是FPGA内线性地址映射的一部分,这样,软件物理器件驱动器能够很容易的读取寄存器。

本文引用地址:http://www.eepw.com.cn/article/80965.htm协处理器的软件物理器件驱动器与硬件寄存器接口相比,具有更高级的抽象功能。软件驱动器实现了系统算法参数到控制寄存器的映射,因此可以很容易的编写和维护应用软件。底层的硬件改变时,高层的模型器件驱动器可以保持不变。Delphi系统中的软件体系提出了几个抽象层,将算法实现从其软硬件物理实现中分离出来,为软件或硬件协处理器算法提供了强有力的支持。FPGA协处理器非常适用于这种Delphi软硬件体系。

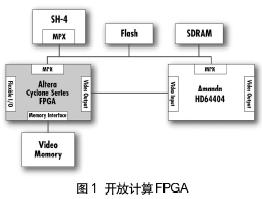

FPGA可以设计应用到许多基本体系和Delphi结构相似的系统中去。这些系统包括一个或者多个控制器或DSP处理器,可以使用FPGA加速实现需要高性能处理的任务。实现FPGA协处理器的关键在于为FPGA设计不同的硬件加速器,外部控制处理器集成硬件加速器,产生进行硬件加速控制的软件层。所需硬件加速器应用包括视频和通信的主流算法。这些应用有广阔的市场,已经开始服务于那些致力于设计标准专用知识产权(IP)硬件加速器的专业公司。这类公司提供通用算法,直接应用到先进的低成本FPGA上。可以直接购买商用MPEG2,MPEG4,H.264,WiFi的IP模块,以及许多其他的视频和通信标准IP模块。图2的例子是Amphion公司的MPEG4解码器IP模块,适用于ASIC或FPGA应用场合。

下一步是在FPGA中集成硬件加速器,利用外部总线进行控制,数据输入和输出。设计者可以使用一种新的开发工具,很容易的实现这种集成。利用来自Altera的系统集成工具--SOPC Builder,设计者从可用的IP列表中选择合适的IP模块。进行选择时,参数化菜单显示不同结构的选项,这些选项由使用者在执行前进行设置。设置好参数后,模块便被包含到别的外设列表中,处理器由工程师进行集成。每个独立IP模块被选择并参数化后,他们将被集成到处理体系中去。

评论