FPGA到高速DRAM的接口设计(04-100)

——

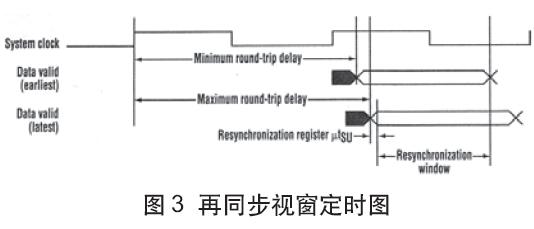

为了得到安全的再同步视窗,设计人员需要计算加上上面所列的所有延迟(称之为往返延迟)系统的最小和最大延迟(见图3)。用下面的方程式可得到再同步视窗:

本文引用地址:http://www.eepw.com.cn/article/80852.htm

再同步视窗=最小往返延迟+1个时钟周期—最大往返延迟—再同步寄存器的最大微建立和/保持时间

若再同步视窗落在系统时钟沿的外面,设计人员需要用另外的相移PLL输出时钟,这沿将会在此视窗内。计算往返延迟和评估再同步时钟的时钟相位易于出错并且耗时。

很多时间,设计人员用不断试验来找出再同步时钟相位。某些FPGA供应商提供设计帮助,可以减少或消除不断试验的过程。例如,Altera的再存储器一控制器IP核具有往返延迟计算器,这可使设计人员计算他们专用系统的再同步视窗。设计人员可以输入迹线延迟和其他专门适于他们系统的其他延迟元件。往返延迟计算器将判断系统时钟和DQS域之间的编移。若需要来自PLL的相移输出,它也可以确定正确捕获数据所需的相移量。

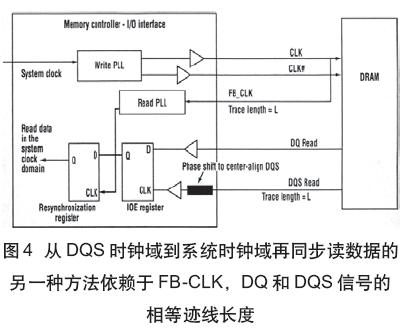

再同步的另一技术是用反馈时钟,另外的Read PLL示于图4。来自存储器的反馈时钟FB-CLK的板迹线应该与DQ和DQS信号的板迹线长度相同。FB-CLK连接到DRAM CLK引脚并返回到FPGA。Read PLL相移输入时钟FB-CLK,所以,它能从DQS域到系统时钟域正确地捕获读数据。相移量是来自DRAM的±TDQSCK,DQS、CLK和FB-CLK迹线之间的任意板迹线偏移和IOE寄存器和再同步寄存器之间的延迟之和。

评论