产品开发过程中的EMC设计

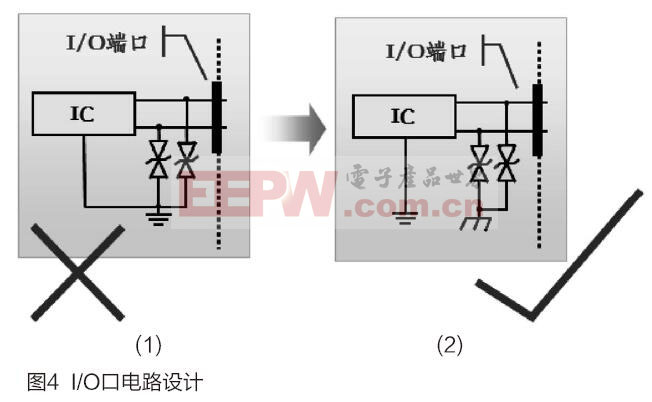

I/O口电路的设计同样受到PCB布局及接地设计的影响。如图4(1)的端口防护器件的接地和后端被保护IC的地进行共地设计,这种设计一旦瞬态脉冲被钳位卸放到地上面,由于这个地同时也是IC的参考地,很容易导致IC地电位抬高而出现异常;改善方案主要有两种:如果系统是两线制设备(无地线)系统外壳也是非金属材质,此地线设计也必须将IC的参考地和防护器件的地分开,不能共用在一起,但是由于此系统属于无地线系统,可以采用这两个部分分别铺设不同的接地区域,然后使用Y电容将两个区域的地线连接在一起。另外一种是系统有设计地线或者外壳属于金属外壳,这种情况就可以将防护器件的接地直接连到外壳地或者通过Y电容连接到外壳地,但是一定要和IC的参考地分开。

本文引用地址:http://www.eepw.com.cn/article/281889.htm

上面提到的PCB走线的设计导致防护电路失效的问题,通过图5就可以看到端口设计了TVS管防护ESD,但是如果布线按照图5(1)这样走线,极易导致IC损坏,但是TVS管还没有动作的,主要是由于现有的ESD或者EFT都是高频干扰,走线阻抗常大,所以对于端口的防护电路设计一定要遵守靠近端口的原则进行设计PCB。

2.3 EMI电路设计

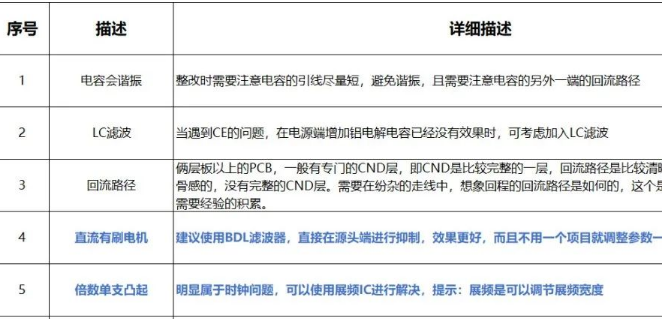

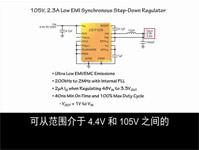

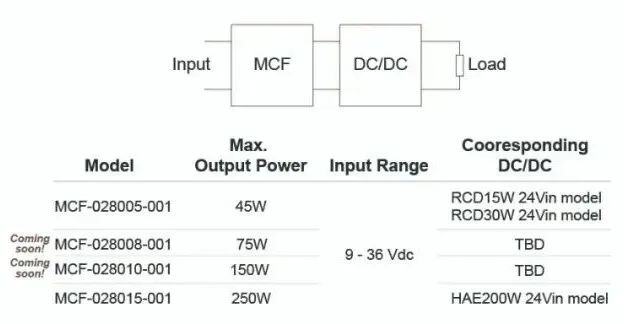

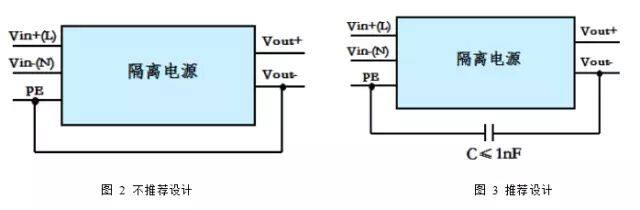

金升阳电源在电磁干扰方面内部增加了滤波电路、屏蔽措施等,保证符合承诺的各项指标要求,但是电源在应用方面还是难免出现电磁干扰超标的问题;此时,很多设计工程师都会认为问题的根源在于电源,这种其实是有误区,因为电磁干扰传导骚扰测试项目,主要是针对电源端口,那么电源端口就成了其传输路迳,所有的电磁干扰都会经过电源端口到达被测设备,测试设备测试到的电磁干扰除了来自电源本身外,主要还包括整机中的其他部分产生的电磁干扰,以及设备内部寄生参数的谐振产生的电磁干扰。电源内部的滤波器无法对这类电磁干扰进行抑制,这些电磁干扰就通过电源端口耦合到测试设备。为了应对千差万别的应用环境,电源厂家设计滤波器时,除了抑制电源内部干扰,还会考虑到滤波器衰减特性及频谱特性,尽量预留最大的设计余量。那么这就要求整机设计人员在设计电源前端时候,一定要按照电源厂家推荐的应用电路进行设计,例如:LH15产品应用过程中出现EMI超标问题(见图6)。

图6为金升阳电源LH15-13B05传导骚扰测试结果,此结果符合EN55022/CISPR22的CLASS B要求,而且余量非常充分。

图7为金升阳电源LH15-13B05的电源应用到某品牌产品上面后,整机测试传导骚扰结果,此结果无法符合EN55022/CISPR22的CLASS B要求,甚至连CLASS A都无法满足要求,更不用说设计余量。

所以电源即使内部电磁干扰设计等级再高,在应用过程中一定要留应用部分,具体参数可参考具体产品对应的规格书。

3 结语

整机电磁兼容设计其实是一个系统性工程,任何一个点设计不到位都可能导致设计失败,甚至会付出沉重的成本代价。目前,行业内对于这方面的设计失败原因局限于电源方面,而忽视PCB设计、结构设计及接地设计等方面。有效解决EMC问题,需要在设计初期就充分评审指标定位、应用环境;在设计过程中充分评审电路图设计、原材料选型、PCB绘制、结构设计、工艺安装等各方面,不断地优化开发流程,实现在开发过程中考量所有问题。

参考文献:

[1]IEC 61000-6-2-2005 通用标准工业环境的抗扰度标准

[2]IEC 61000-6-4-2007 通用标准工业环境发射标准

[3]IEC 61000-4-2-2006静电放电抗扰度试验

[4]IEC 61000-4-4-2008 电快速瞬变脉冲群抗扰度试验

评论