如何实现软件定义无线电动态范围的最大化

在为接收器设计设置级联噪声系数和截距模型时,您实际上需要为系统建模三次: 一次针对最小信号电平,即最大增益下的AGC关闭电平;第二次针对最大信号电平,即最大增益衰减下的AGC开启电平;最后一次针对接收器的标称输入电平。 您还需要在所有三种模型中考虑交调效应。 幸运的是,ADI的ADISIMRF(图1)等免费工具将助您一臂之力;这类工具通常内置适用于RF增益块、混频器、衰减器、巴伦、滤波器和高速转换器的模型库。

本文引用地址:http://www.eepw.com.cn/article/279224.htm

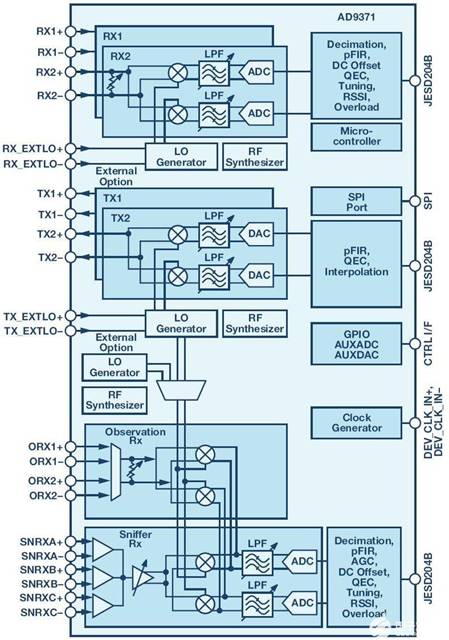

频率规划是另一项需要广泛研究的有趣课题。 您不仅需要为每个混频器(图2)制作一个混频器表,而且可能还希望为发射路径制作一个类似的DAC表。 此外,您还需要考虑在哪个奈奎斯特频率区域使用转换器(ADC或DAC)。 系统时钟通常是帧速率的倍数(这就是1.2288 MHz和13 MHz的倍数之所以常见的原因)。 幸运的是,您可以使用足够高的频率(谐波不在频带范围内或目标信号上)。 您需要通过精心挑选系统时钟、中频和本振(LO)频率来最大程度地减少内外部干扰,因为这些频率将与无法预见的后果混合。

针对级数和功能类型(滤波器、混频器、放大器等)设置了级联噪声系数和截距模型后,就需要执行一些端计算。

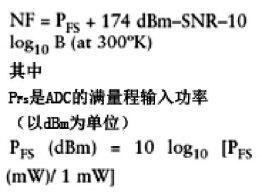

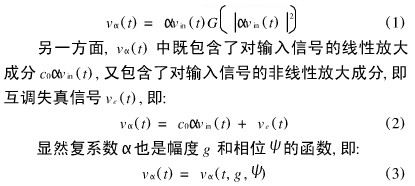

例如,您首先需要使用以下等式计算ADC的噪声系数(NF):

NR是ADC的信噪比(以dB为单位) ,以及 B是要进行数字转换的带宽,需要考虑输入滤波器的噪声带宽(图3)。

请注意,如果您希望将所需信号加上干扰信号进行数字转换以滤除数字域中的干扰信号,此带宽可能比信号带宽更宽。

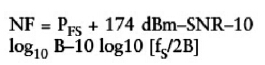

幸运的是,您可以通过对输入信号过采样来提高ADC的噪声系数。在这种情况下,计算噪声系数的等式将变为:

其中,fS是采样时钟,B仍然是信号带宽(或要进行数字处理的带宽)。 一些IF采样ADC(如AD9874和AD9864)会在带通Σ-Δ架构中使用过采样和噪声整形。 这些ADC实际上是完整的IF子系统,接受IF输入并提供接近100 dB的SNR,以及在输出时抽取的16或24位I和Q数据。

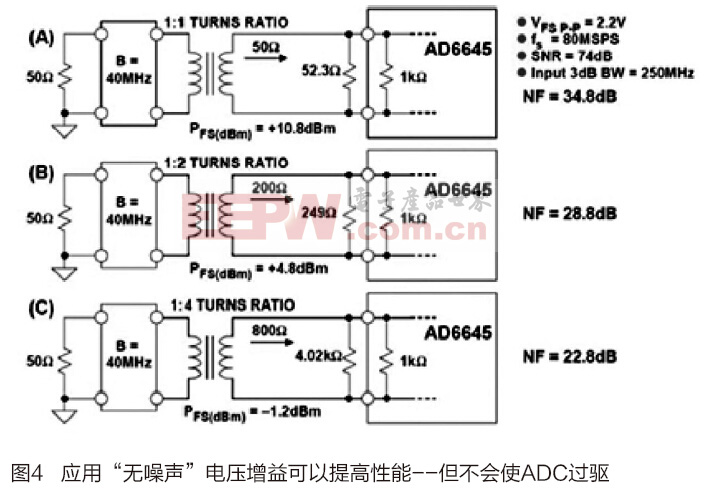

过采样并不是改善ADC噪声系数的唯一途径。您也可以使用变压器在“无噪声”增益下提高ADC的输入电压,如图4所示AD6645。

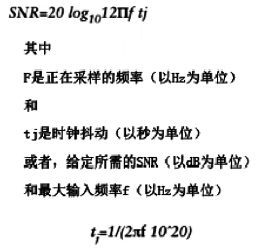

您需要完成的最后一个端计算是针对转换时钟的。具有(或缺乏)生成低抖动时钟的能力是针对高动态范围的接收器未在天线中放置ADC的原因所在,我们将在下面对此进行介绍。 计算ADC理论上的SNR(作为时钟抖动的函数)的等式为:

例如,在进行IF采样时,如果您希望在IF为240 MHz时对20 MHz宽的信号采样,则频率最高的采样元件将是IF加上信号带宽的一半(或250 MHz)。SNR为80 dB,最大输入频率为250 MHz时,可通过求解得出最大时钟抖动为63.66 fs。您可以仿真PLL/VCO的性能,并使用以下网址提供的ADISIMPLL和ADISIMCLK等免费工具计算各类环路滤波器以及电路配置的抖动:www.analog.com。 借助这些工具,您可以优化环路滤波器的设计以获得最佳相位噪声,进而最大程度地减少抖动,这种做法的代价是会增加滤波器的建立时间,但这对高速ADC的固定频率时钟来说通常不是问题。

模拟信号相关文章:什么是模拟信号

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

漏电开关相关文章:漏电开关原理

评论