精确估算SoC设计动态功率的新方法

通过省去基于文件的流程,新工具可提供完整的 RTL 功率探测和精确的门级功率分析流程。

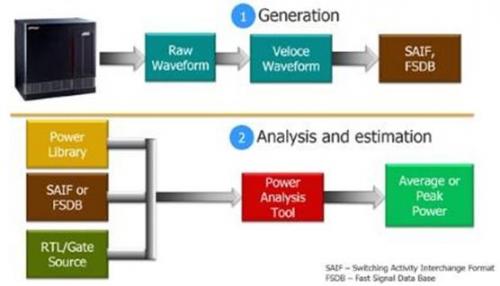

本文引用地址:http://www.eepw.com.cn/article/278132.htm在最近发布的一篇文章中,笔者强调了当前动态功耗估算方法的内在局限性。简单来说,当前的方法是一个基于文件的流程,其中包括两个步骤。第一步,软件模拟器或硬件仿真器会在一个交换格式 (SAIF) 文件中跟踪并累积整个运行过程中的翻转活动,或在快速信号数据库 (FSDB) 文件中按周期记录每个信号的翻转活动。第二步,使用一个馈入 SAIF 文件的功率估算工具计算整个电路的平均功耗,或使用 FSDB 文件计算设计时间和空间内的峰值功率(见图 1)。

图 1. 传统的功率分析根植于基于文件的两步法。

当被测设计 (DUT) 相对较小(约数百万门或更少),且分析周期较短(不超过百万个时钟周期),这些方法可能行得通。上述时间窗口常见于自适应性功能验证环境。

然而,如今的大型 SoC 设计具有数千万或数亿个门来执行嵌入式软件(比如,启动一个操作系统或运行需要数十亿个周期的应用程序),若使用传统方法就会面临以下三大难题:

1. SAIF 文件将变得太过庞大而无法管理,FSDB 文件则更是如此。

2. 文件生成过程慢如蜗牛,短则数小时,长则超过 1 天。

文件加载到功率估算工具的速度也相当缓慢,少则几天,多则超过 1 周。

这一切似乎注定了无法成功。

评论