平面架构1x纳米NAND揭密!

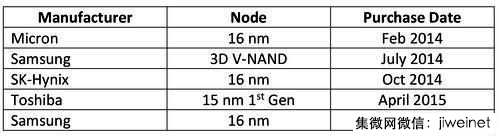

过去的一年半以来,主要NAND快闪记忆体制造商已经开始销售1x奈米等级的平面快闪记忆体;根据我们调查开放市场上所销售元件的供应来源,美光(Micron)是从2014年2月开始供应1x奈米元件的第一家记忆体厂商,随后是在同年10月推出产品的SK海力士(Hynix)。在近六个月之后,TechInsights实验室才出现三星(Samsung) 16奈米与东芝(Toshiba) 15奈米产品。

本文引用地址:http://www.eepw.com.cn/article/276172.htm针对平面NAND快闪记忆体的微影尺寸终点,在文献中已经有很多讨论;其替代方案是垂直堆叠式的快闪记忆体,例如三星的3D V-NAND与东芝的BiCS。业界有一个共识是平面NAND将在差不多10奈米节点终结,也就是目前TechInsights刚完成分析的15/16奈米NAND快闪记忆体的下一代或两代。因此我们认为,现在正是来看看这些15/16奈米快闪记忆体的一些制程特征的时候。

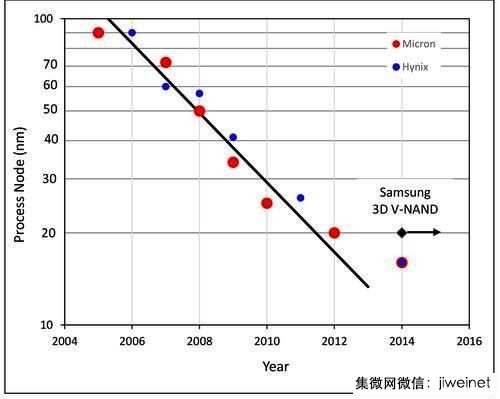

不同年份的美光与海力士NAND记忆体制程节点 (来源:TechInsights)

TechInsights这几年来为了拆解分析报告买过一些NAND快闪记忆体,下图是我们从美光与SK海力士所采购之NAND快闪记忆体的年份与制程节点对照;这两家通常是最快推出最新制程节点产品的记忆供应商。半对数图(斜线)显示,美光与海力士每一年的NAND制程节点通常约微缩23%。

TechInsights采购过的1x奈米等级NAND快闪记忆体(来源:TechInsights)

制程微缩速度在25奈米节点以下显着趋缓,这可能反映了实现双重曝光(double patterning,DP)微影与减少相邻记忆体单元之间电气干扰的困难度。DP有两种方法:LELE (Litho-etch-litho-etch)通常运用在逻辑制程,而利用侧壁间隔(sidewall spacers)的自对准双重曝光(self-aligned double patterning,SADP)则被记忆体业者所采用。

但到目前16奈米节点的NAND快闪记忆体元件可适用以上方法,10奈米以下元件恐怕就无法适用。微缩至平面10奈米制程的NAND快闪记忆体仍然遭遇显着的挑战,这也促使厂商着手开发3D垂直NAND快闪记忆体。如上图所示,我们也将三星的首款3D V-NAND纳入,不久的将来东芝、海力士与美光也可能会推出3D NAND快闪记忆体产品。

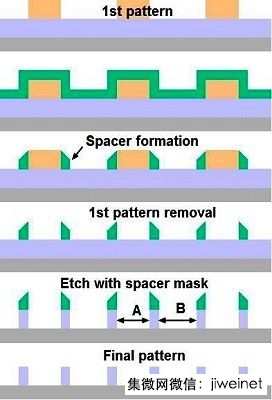

双重曝光已经成为生产16奈米NAND快闪记忆体的必备技术,记忆体制造商使用SADP以完成活性、控制闸、浮动闸以及位元线曝光;SADP制程的步骤,从初始曝光经过侧壁间隔蚀刻,回到第二重曝光,如下图所示。

自对准双重曝光制程(来源:Wikipedia、TechInsights)

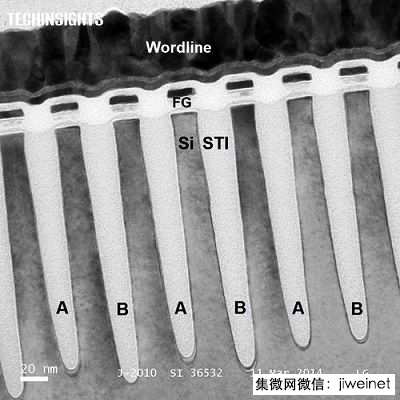

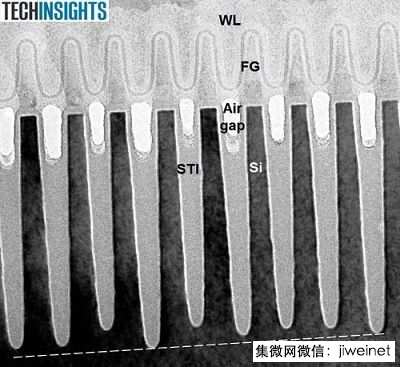

双重曝光微影制程通常会导致最终的侧壁间隔结构之间的空间不对称,被视为一种AB图案(AB patterning),这可以从下图美光16奈米NAND快闪记忆体的浅沟槽隔离(shallow trench isolation ,STI)图案轻易看出。

美光的16奈米NAND快闪记忆体矽通道与STI (来源: TechInsights)

图中可看到一条钨(tungsten)金属字元线(word line)从左至右横过一连串与底层矽通道对齐的浮动闸结构上方;浮动闸与矽通道已经采用SADP制程一起进行图案化与蚀刻,STI底部与相邻的矽通道之间,在其蚀刻深度展示了AB图案特性,并显示使用了SADP技术。

SK海力士在其M1x奈米浮动闸NAND快闪记忆体(于2013年IEDM会议上发表),使用的是四重间隔曝光(quad spacer patterning)技术,如下图所示;沟槽底部的AB图案几乎是不存在,而是被更随机的图案所取代。我们可以在三星的16奈米与东芝的15奈米NAND快闪记忆体看到类似的随机图案,也许这意味着他们都是使用四重间隔曝光制程。

海力士的的16奈米NAND快闪记忆体矽通道与STI (来源: TechInsights)

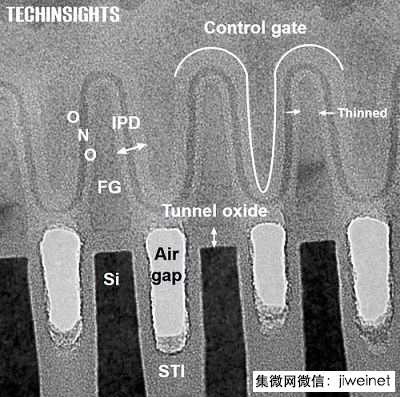

接下来的设计问题是维持控制闸(control gate,CG)与浮动闸(floating gate,FG)之间的高电容耦合,同时将相邻记忆体单元之间的电容耦合最小化。传统上,CG是被FG的三侧所包围,如下图所示。层间介电质(interpoly dielectric,IPD)提供了CG与FG之间的电容耦合,因此需要优异的电流阻挡特性,以及高介电常数K。

下图也可看到海力士的氧化物-氮化物-氧化物(oxide/nitride/oxide,ONO)层;IPD相当厚,减少了CG填补相邻FG的间隙。海力士已经将FG侧边薄化,以提供更多空间给CG;不过要利用这种方式持续微缩NAND快闪记忆体单元间距是有限制的,因为CG得维持被FG的三侧所包围。我们也注意到海力士在矽通道之间加入了活性气隙(active air gap),以降低其电容耦合。

海力士的16奈米快闪记忆体控制闸包裹(Wrap) (来源: TechInsights)

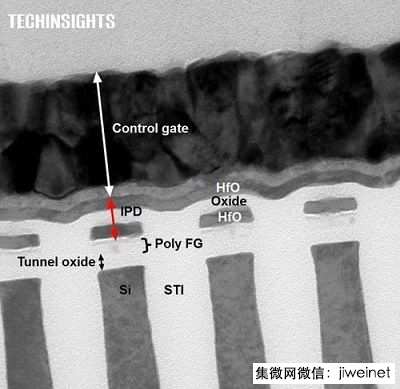

美光已经在16奈米NAND快闪记忆体避免采用包裹式(wrap-around)的CG,转向平面式的CG与FG结构;这并非该公司第一次采用平面闸结构,我们在美光20奈米NAND快闪记忆体产品也观察到该种架构,如下图所示。

美光保留了多晶矽浮动闸,但它看起来不是很薄,这让二氧化铪(HfO2)/氧/ HFO2层间介电质几乎是平躺在浮动闸上方,而HFO2层之间非常高的介电常数,能让CG与FG之间产生足够的电容耦合,免除了海力士、三星与东芝所采用的包裹式闸极架构。

美光的16奈米快闪记忆体控制闸包裹(来源:TechInsights)

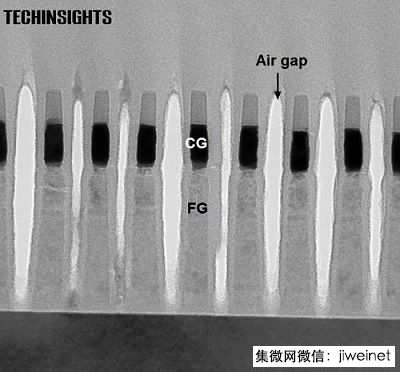

字元线与位元线间距的微缩,加重了相邻记忆体单元之间的电容耦合;这会是一个问题,因为一个记忆体单元的编程状态可能会与相邻记忆体单元电容耦合,导致记忆体阈值电压(threshold voltages,VT)被干扰,或是位元误读。在相邻字元线使用气隙以降低其电容耦合已经有多年历史,下图显示的案例是东芝第一代15奈米NAND快闪记忆体。

东芝15奈米16GB NAND快闪记忆体浮动闸气隙(来源:TechInsights)

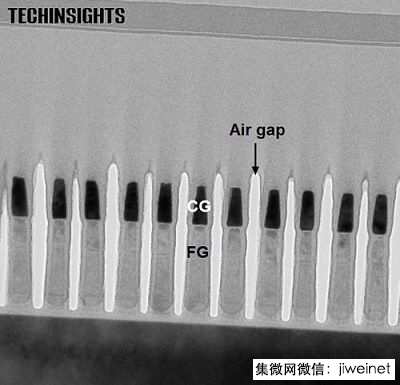

三星16奈米NAND所使用的浮动闸气隙如下图所示,那些气隙的均匀度不如东芝元件,这意味着三星的记忆体单元会显示单元与单元之间串扰的更大可变性,而且可能使得单元写入与抹除时间增加。

三星的16奈米NAND浮动闸气隙(来源:TechInsights)

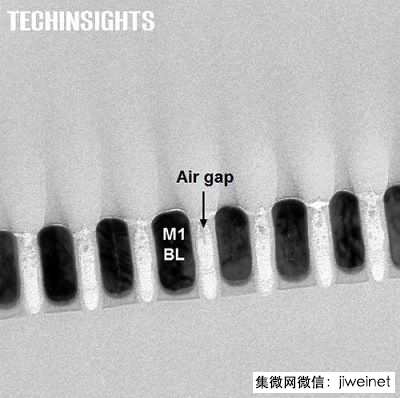

气隙并不限于活性基板(active substrate)与字元线,美光也在16奈米NAND快闪记忆体采用的metal 1位元线采用了气隙,如下图所示。平面NAND快闪记忆体持续微缩之机会,似乎随着浸润式微影以及四重曝光可能只能达到低1x奈米节点而受限;而气隙已经被广泛使用于抑制记忆体单元与单元之间的干扰。

美光的16奈米NAND位元线气隙(来源:TechInsights)

三星、海力士与东芝采用的闸包裹结构可能微缩至到10奈米节点,美光的平面浮动闸技术则能达到次10奈米节点。不过到最后,NAND快闪记忆体将会走向垂直化结构;在此三星是第一个于2014年夏季推出3D V-NAND产品的业者。

评论