基于高速ADC的技术文献及设计方案汇总,软硬件协同

ADC,Analog-to-Digital Converter的缩写,指模/数转换器或者模拟/数字转换器。是指将连续变量的模拟信号转换为离散的数字信号的器件。真实世界的模拟信号,例如温度、压力、声音或者图像等,需要转换成更容易储存、处理和发射的数字形式。模/数转换器可以实现这个功能,在各种不同的产品中都可以找到它的身影。

本文引用地址:http://www.eepw.com.cn/article/274419.htm本文讨论闭环系统的关键要素,重点关注模/数转换器(ADC)和数/模转换器(DAC)的关键角色。文章介绍多片高速ADC和DAC作为控制系统核心的关键作用和性能优势。最后,我们以MAXREFDES32和MAXREFDES71参考设计为例,介绍隔离电源和数据子系统在工业闭环中的应用。

本文将探讨运用时序交错式类比数位转换器时所出现的技术挑战,并对此提供实用的系统设计解决方案。本文也将说明可以解决目前已知问题的创新元件的特色及设计技术。

本文基于TSMC 0.25μm CMOS工艺,设计了一个具有高增益、高带宽的OTA,并且利用该OTA构造一个适用于10位,100 MS/s的流水线ADC的采样保持电路。文章讨论了适宜采用的跨导运算放大器的结构以及对其性能产生影响的因素和采样保持电路的结构,最后给出了仿真结果。

高速ADC的性能特性对整个信号处理链路的设计影响巨大。系统设计师在考虑ADC对基带影响的同时,还必须考虑对射频(RF)和数字电路系统的影响。由于ADC位于模拟和数字区域之间,评价和选择的责任常常落在系统设计师身上,而系统设计师并不都是ADC专家。

本文中的参考设计将采用ADC083000/B3000。时钟源是高速数据转换系统中最重要的子电路之一。这是因为时钟信号的定时精度会直接影响ADC的动态性能。为了将这种影响最小化,ADC的时钟源必须 具有很低的定时抖动或相位噪声。

本文解释了数字反馈,并讨论了一种新的创新性 ADC,这种 ADC 内置了一些功能,在良好设计的布局也许不足以解决问题的情况下,这些功能可用来克服数字反馈。

本文以MAX1124 (Maxim近期推出的250MHz、10位高IF ADC)为例,讨论不同的端接架构以及对高速ADC增益平坦度和动态范围的影响。

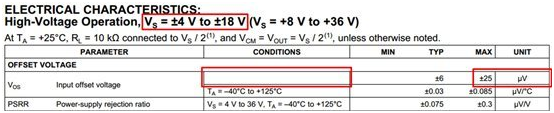

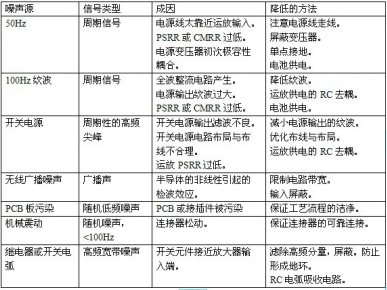

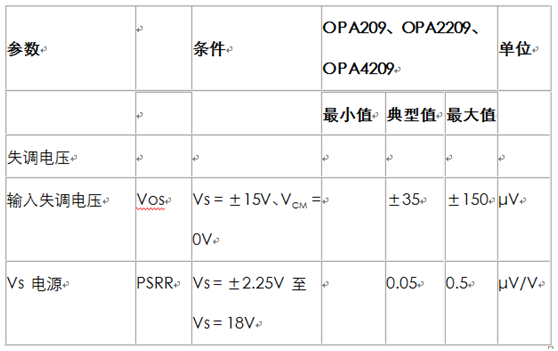

本文介绍对于了解高速ADC电源设计至关重要的各种测试测量方法。为了确定转换器对供电轨噪声影响的敏感度,以及确定供电轨必须处于何种噪声水平才能使ADC实现预期性能,有两种测试十分有用:一般称为电源抑制比(PSRR)和电源调制比(PSMR)。

本文详细介绍了一种高 速A/D转换芯片AD9225的结构和应用,在比较了各种高速数据采集系统的存储方案的基础上,给出了AD9225与628512存储器的接口电路。该电路实际上是高

速ADC与一般RAM接口的缩影。在写信号的实现上,采用了控制逻辑,具有创新性和通用性。

输入共模电压范围(Vcm)对于包含了基带采样和高速ADC的通信接收机设计非常重要,尤其是采用直流耦合输入、单电源供电的低压电路。对于单电源供电电路,馈送到放大器和ADC的输入信号应该偏置在Vcm范围以内的直流电平,能够消除放大器和ADC设计的一大屏障,因为不必在0V保持低失真和高线性度。

评论