基于FPGA+DDS的正弦信号发生器的设计

2.2相关电路设计

本文引用地址:http://www.eepw.com.cn/article/272867.htm2.2.1 D/A转换电路

位于波形输出ROM后的D/A单元,是将数字量形式的波形幅值转换成所要求的合成频率的模拟量形式信号[4].由于储存波形的ROM具有10 bit的输出,所以采用10 bit的DAC将FPGA输出的数字信号转换成模拟信号。本系统采用ADI公司的10 bit COMS数模转换芯片AD5432,AD5432的驱动电压为3 V~5.5 V,具有50 MHz的串行接口、10 MHz的乘法带宽、2.5 MS/s的更新速率,采用±10 V的参考输入,输出为电流[5].

2.2.2滤波电路

经由DAC的输出信号实际上是阶梯模拟信号,需利用低通滤波器滤除波形的杂波,并进行平滑处理。由于本系统的最高输出频率为10 MHz,所以选取的低通滤波器的截止频率也应为10 MHz.为了减少系统体积,节省设计时间,提高系统的可靠性,本系统选用凌特公司LT6600-10低通滤波器。LT6600-10内集成了一个全差分放大器和一个近似于切比雪夫响应的四阶10 MHz低通滤波器,差分增益由两个外部电阻设置[6],其基本连接方式如图3所示。

图3 LT6600-10 的基本连接方式

3实验仿真与分析

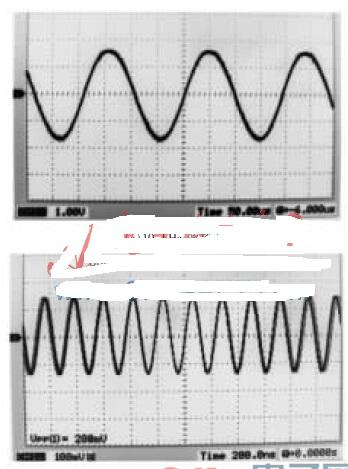

实验中所用的FPGA芯片为Altera公司的Cyclone III系列,Cyclone III是Altera公司的首款65 nm低成本FPGA,含有5 K~120 K逻辑单元(LE),288个数字信号处理(DSP)乘法器,存储器达到4 Mbit.Cyclone III系列比前一代产品每逻辑单元成本降低20%,使设计人员能够更多地在成本敏感的应用中使用FPGA.系统所用的测试频率(参考频率)为50 MHz,调试好系统,使系统的输出从1 kHz~10 MHz递增,并改变输出波形的相位,输出波形的相位变化范围为0°~360°。经示波器测试,系统的输出波形形状良好,输出波形的实测频率与理论计算值的绝对误差小于0.1%,满足设计要求,有较好的实用价值。图4为实验的输出波形。

图4 实验输出波形

产生测试信号的仪器统称为信号源,也称为信号发生器,它用于产生被测电路所需特定参数的电测试信号。信号发生器用途非常广泛,科学实验、产品研发、生产维修、IC芯片测试中都能见到它的身影,目前市场上大部分信号发生器多采用DDS频率直接合成技术。尽管基于FPGA的DDS信号发生器应用广泛,较传统的信号源有许多优点,但是由于DDS数字化实现的固有特点,决定了其输出频谱杂散较大,又由于DDS内部DAC和ROM的工作速度的限制,使得DDS信号源的最高输出频率受限[7].不过,随着DDS技术的不断完善和发展,其频谱杂散、最高输出频率的性能指标将得到优化,未来将有越来越多的信号发生器采用DDS技术,所以说对DDS进行研究具有很好的现实意义。

低通滤波器相关文章:低通滤波器原理

负离子发生器相关文章:负离子发生器原理 数字滤波器相关文章:数字滤波器原理 离子色谱仪相关文章:离子色谱仪原理

评论