FPGA设计开发软件ISE使用技巧之:编译与仿真设计工程

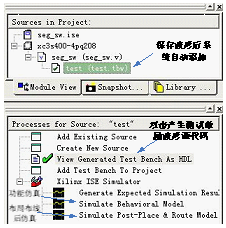

波形图编辑完毕后,单击“保存”按钮,系统会为工程自动添加“test.tbw”文件。选中此文件,在当前资源操作(Process for Source)视窗中,可以看到“View Generated Test Bench As HDL”选项,如图6.25所示。

本文引用地址:http://www.eepw.com.cn/article/269336.htm

图6.25 生成测试激励波形文件后的资源视窗

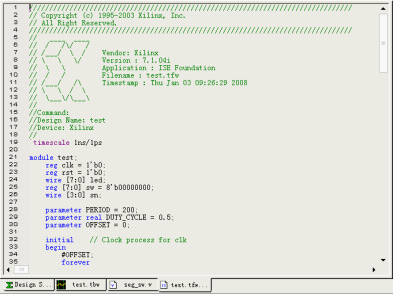

双击此选项,系统就会根据设置的波形自动生成测试激励文件的源代码,如图6.26所示。

图6.26 系统根据编辑的波形生成的测试代码

(3)对设计工程进行功能仿真。

ISE Simulator中提供了两种级别的仿真:功能仿真和布局布线后仿真,功能仿真可以验证代码功能的正确性,布局布线后生成的仿真时延文件包含的时延信息最全,不仅包含门延时,还包括实际布线延时,所以布线后仿真最准确,能较好地反映芯片的实际工作情况。

按上述步骤用HDL Bencher生成测试激励波形文件后,就可对设计工程进行仿真了,首先验证设计功能的正确性,先对工程进行功能仿真。

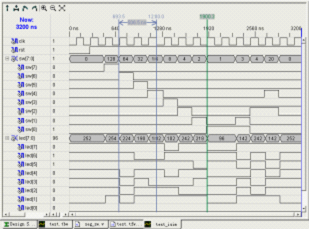

功能仿真时在工程资源(Sources in Project)视窗中选择波形文件(test.tbw),在当前资源操作(Process for Source)视窗中,双击Simulate Behavioral Model(如图6.25所示),得到功能仿真结果如图6.27所示。

图6.27 功能仿真结果

观察波形时,左上角有几个按键。单击![]() 可放置一条线,用于观查某一特定时刻的值。

可放置一条线,用于观查某一特定时刻的值。![]() 用于测量时间间隔。

用于测量时间间隔。![]() 用于寻找前一个或下一个信号上升沿,主要用于在测量时间间隔时,定位测量直线。

用于寻找前一个或下一个信号上升沿,主要用于在测量时间间隔时,定位测量直线。

另外,ISE Simulator在仿真过程中会自动判断仿真过程中是否会有错误发生,如果有错误发生,会在TX_ERROR下显示出来,TX_ERROR会自动统计错误的个数并显示,并且在SimConsole信号视窗中显示正确的数值和实际仿真得到的数据,用户可根据这些信息,对源代码进行修改。

(4)布局布线后仿真。

功能仿真测试功能正确后,就可以按照ISE下FPGA的设计流程对工程进行综合及布局布线。布局布线后,就可以对工程进行布局布线后仿真。

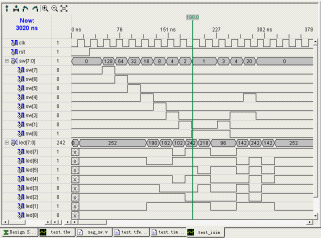

布局布线仿真时在工程资源(Sources in Project)视窗中选择波形文件(test.tbw)。在当前资源操作(Process for Source)视窗中,双击Simulate Post-Place&Route Model(如图6.25所示),得到布局布线后仿真结果如图6.28所示。

图6.28 布局布线后仿真结果

如图6.28所示,布局布线后仿真结果与功能仿真结果相比,有了较大的延迟,这主要与代码中组合逻辑设置有关,在布局布线仿真后,由于加入了延时信息可能会造成功能的不正确,用户可以通过改写代码或添加相应的时序约束,来优化设计,布局布线后仿真在工程设计中占有很重要的地位,需要花很长时间来不断地仿真和优化设计。

3.小结

本节通过一个具体的实例介绍了ISE下自带仿真工具ISE Simulator的使用。ISE Simulator的特点是可以通过HDL Bencher在图形界面下编辑波形,不需要用户编写测试代码,使用方便。用户也可以在HDL Bencher下完成波形编辑生成测试代码后,调用ModelSim仿真。

通过这个例子,希望用户能够掌握ISE Simulator的基本用法,熟悉仿真的基本流程。仿真在FPGA的设计当中占有很重要位置,可以说设计者的大部分工作都是在做仿真,只有仿真结果达到要求了,才会映射到实际电路,然后在线调试。

在这里推荐大家自己编写测试激励文件。因为在一些复杂的设计当中,使用图形界面编辑激励波形是很难满足设计要求的,无法对工程进行完整的测试。

另外,ModelSim是一款功能很强大的仿真软件,支持混合仿真。在ISE下为ModelSim预留了接口,使用也很方便,目前应用比较广泛。在初始学习阶段可以使用ISE Simulator作一些简单的仿真,熟悉FPGA的设计流程,等熟练之后,建议在ModelSim下完成仿真。

fpga相关文章:fpga是什么

评论