【从零开始走进FPGA】美好开始——我流啊流啊流

2. 仿真必备的知识

本文引用地址:http://www.eepw.com.cn/article/268641.htmAltera_Modelsim仿真资料:http://www.chinaaet.com/lib/detail.aspx?id=86257

四、配置FPGA

1. 配置综合

配置引脚简单的说就是通过软件的设置,将FPGA内部逻辑信号映射到IO上,具体有下面几种方法:

(1)在Assignments-Pin Planner中对应IO手动输入IO引脚

(2)Quartus II Tcl Console 手动输入,输入的格式为:“set_location_assignment PIN_28 -to clk”

(3)Tcl Scripts,通过调入tcl 文件来进行映射

(4)在Assignments-Import Assignments,通过调入(2)格式的文件来进行映射。

后面两种方法具体步骤可见网友“小时不识月”的网页教程:http://www.cnblogs.com/yuphone/archive/2010/01/18/1650612.html

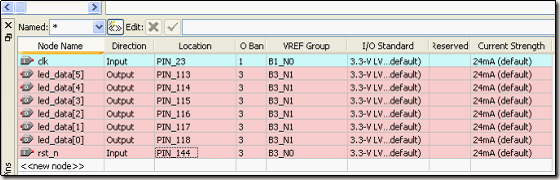

配置好查看Quartus II Pin Planner,如下图所示:

配置完引脚在进行综合,就少了上述提醒没有进行引脚配置的2个警告。

注意1:对于Quartus II 中引脚配置的方法,若用最原始的第一种GUI手动输入配置,需要第一次编译后让软件在Pin Planner生成IO,然后再GUI下手动配置;若用其他三种方法,可以在第一次编译以前,用命令输入配置信息,在Quartus II 编译后,自动识别映射信息,达到同样的效果。

注意2:对于系统及的FPGA设计,由于工程之大,引脚之多,一般编译综合需要耗费很大的时间,因此一般采用不采用第一种方法,而且在第一次编译以前事先导入映射信息。

2. 目标板下载模式

总而言之,Quartus II 软件只是个GUI的 用户终端,用来设计代码,综合FPGA逻辑电路,最终的目的,是通过USB Bluster、并口或者其他途径下载到目标板。具体有以下几种:

(1)配置FPGA——JTAG Mode

所谓配置FPGA就是将sof文件电路配置FPGA的SRAM(FPGA是基于SRAM格式的),在不掉电的情况下进行现场配置,验证。此方式是通过JTAG接口下载的。

(2)烧录EPCS——Active Serial Programming

所谓烧录EPCS是生成的代码信息烧录到存储芯片EPCS中,通过配置信号或者重新上电,配置FPGA SRAM;由于EPCS flash结构,因此EPCS中的掉电不丢失(类似于CPLD)。烧录EPCS有两种方法,如下

a) 通过ASP接口下载pof文件

b) 通过JTAG接口下载jic/jam文件,jic/jam文件由Quartus II 软件对sof文件进行转换后得到。

(3)Passive Serial并口下载

(4)In Socket Programming下载

以上两种模式,由于应用不是很广泛,在此不做过多阐述。

综上说明,在成本敏感,或者电路板空间苛刻的情况下,完全可以舍去ASP接口,而用JTAG来替换。考虑到Altera设计了两种接口的原因,是给用户更大的选择性,特殊场合下,可以只存在ASP接口,只进行一次烧录,而不用JTAG接口进行测试。

3. JTAG的下载

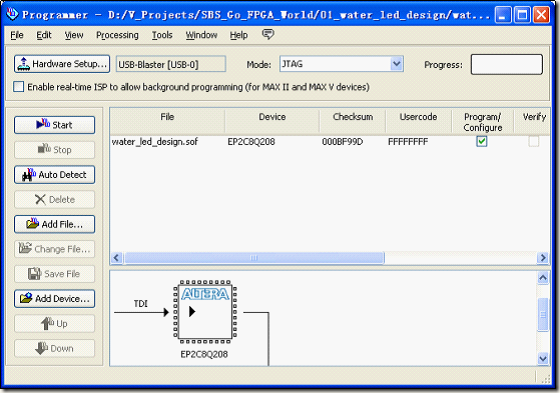

(1)在工具栏打开或者菜单栏Tool打开Programming

(2)若没找到Hardware,在Hardware Setting中找到USB Bluster。

(3)选择JTAG Mode

(4)若没有自动加载sof文件,点击Add File导入该工程的sof文件

(5)最后点击Start,等待下载完毕,如下图所示:

fpga相关文章:fpga是什么

c++相关文章:c++教程

评论