【从零开始走进FPGA】美好开始——我流啊流啊流

3. 代码编译

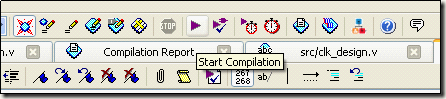

本文引用地址:http://www.eepw.com.cn/article/268641.htm(1)通过Processing-Start Compilation,或者工具栏的图标如下:

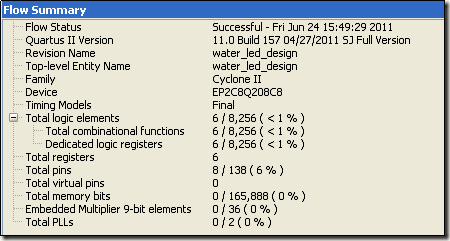

(2)编译结果如下,可见相关信息:

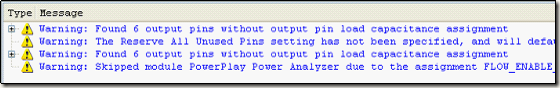

(3)警告的分析及解决:

a) Warming(4)如上图所示,具体解释如下:

i. 没有电容配置

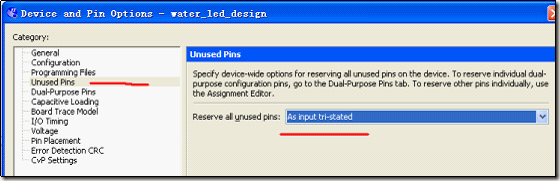

ii. 没有把unused的pin设置为三态。在Assignment-Device-Device and Pin Opitions-Unused Pins,设置如下图所示:

iii. 没有电容配置

iv. 可以忽略

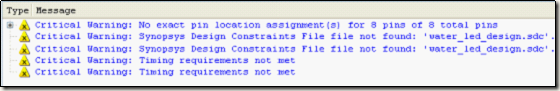

b) Critical Warming(5)如上图所示,具体解释如下:

i. 引脚没有分配IO

ii. 没有sdc时序约束文件

iii. 没有sdc约束文件

iv. 时序没有达到要求

v. 时序没有达到要求

出现这些警告的原因是因为Quartus II 10.1以后的版本软件,不再自带TimeQuest Timing Analyzer,只有Classic Timing Analyzer,虽然不加sdc时序约束对于一般情况也不一定会有错,但软件设计的必然会出现这样的警告。关于TimingQuest sdc,会在后续章节中阐述,此处不做具体说明。

关于Quartus II 警告信息分析以及零警告的处理,可以右击警告查看help,altera会告诉您相应的解决方案;此外,Bingo已上传Chinaaet“Quartus II 警告分析.pdf”,下载地址为:http://www.chinaaet.com/lib/detail.aspx?id=86271

初学折有不到之处可以查阅该pdf,记住,永远不要轻易忽略警告。

三、Modelsim-Altera仿真

1. 为什么要仿真

首先讨论两个问题:

(1)仿真?是真的吗?

仿真,只是为了模拟真实现象,测试代码的行为以及时序的正确性;当然,仿真永远是模仿的,不可能是绝对准确的,只能在一定程度上模拟真实时序,让我们的设计变得更可靠。仿真对于电路设计者,只是一个软件测试的平台,而不是实际硬件设施的测试结果。

(2)一定要仿真吗?

未必!如果你有足够的把握时序的准确性,脑子里能够完成整个电路的时序逻辑工作流程,仿真就不是那个必须的了;对于已经成型的模块,保证时序准确的情况下,何必在徒劳的仿真呢?按常理,是现有Quartus II软件,再有仿真软件的吧,Testbench只是测试程序,链接两者之间的桥梁。

回想,在n年前的老工程师,用block中用与非门与74系列芯片设计的原理图,要仿真似乎变得很难?那些老前辈们是通过实物的测试,不断的修正、改善,最后才得到可靠的电路。

因此,仿真 不是必须的。Bingo就经常不仿真!不是说懒,是因为脑子中的电路时序逻辑,本能性的能够保证电路的准确性,或者说出了问题能够自行改正,不会失去了方向。所谓代码在电脑上,电路在脑子中,每一句行为级语言,都加增添一个电路。

当然,并非每一个人都可以这样子的。对于初学者而言,仿真是非常重要的一个过程。原因是因为在初学者脑子中,还未呈现固定逻辑实现的时序工作流程,换句话说,经验不够丰富吧。

当然在时序很复杂而且庞大时,时序仿真是必须的,因为在这种情况下,大脑的模拟也许无法跟计算机的计算速度比拟了。

前文安装Quartus II 软件章节有提到过,Quartus II 9.1以前版本,软件自带仿真器,而9.1以后的版本,需要第三方软件的支持。第三放仿真软件有很多,而用的最多的,固然是Modelsim-Altera。本章节中Quartuus II 11.0与Modelsim-Altera协同工作,仿真测试本例程的代码的时序。希望通过节的分析,对时序逻辑上有一个更深刻的认识。

fpga相关文章:fpga是什么

c++相关文章:c++教程

评论