基于CPLD技术的CMOS图像传感器高速采集系统

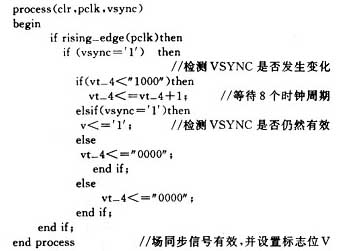

首先按顺序检测VSYNC和CHSYNC信号是否有效,应该注意的是要防止毛刺信号干扰。由于毛刺信号时间很短,故在本设计中采用了设标志位的方法,即当检测信号有效沿后(对于VSYNC是上升沿,而对于CHSYNC是下降沿),在等待一定时间后再次检测信号,看其是否仍然有效,如果有效,则说明信号是正确的。其源程序如下:

由于象素数据按照PCLK时钟输出,所以用来存储图像的RAM的使能信号RCE和写信号RWE、读信号RRE以及地址信号ADDRESS都是由CPLD用他来产生。其中,读信号RRE在CPLD写操作中置“1”即可。由于在数据输出时,PCLK上升沿信号稳定,而RAM是在WR上升沿将数据写入,因此可以在HREF有效后(HREF=1)采用PCLK作为写信号RWE。同时设计一个二进制计数器,在HREF有效后,以PCLK的下降沿为触发沿对PCLK做计数,并取其输出作为RAM的地址信号ADDRESS。这样在PCLK的下降沿更新地址信号,接着在上升沿存贮数据。源程序如下:

设置往RAM写信号RWE

由于图像象素点个数已知,即数据个数已知,故在计数完毕后CPLD发出计数完毕信号R,同时把指向RAM地址线ADDRESS和读写信号RWE、RRE切换连至AT89C51的地址线和读写信号WR、RD。AT89C51接受到中止信号R后开始读取RAM中的数据,并通过RS232串口上传至PC机。需要注意的是RAM地址达到512 k,而单片机最大寻址空间只有64 k,所以在读取RAM时采用分页读取,每次读64 k,即从P1口中抽取3根线作为RAM的最高的三位地址和P0和P2口共同组成AT89C51的地址线。

2、结语

采用CPLD对CMOS图像传感器进行数据采集的方法,可以把CMOS的主动器件通过CPLD变为可控制的方式,实现了对CMOS图像传感器的高速数据读取,按照该方法制作的系统,经过实验验证效果良好。这种信号读取的方法还可以在其他诸多需要高速图像数据采集的场合应用

传感器相关文章:传感器工作原理

风速传感器相关文章:风速传感器原理 上拉电阻相关文章:上拉电阻原理

评论