FIR滤波器设计方案汇总,包括FPGA、DSP、MATLAB等架构

FIR滤波器,有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。本文着重介绍基于不同结构的FIR滤波器的设计方案,供大家参考。

本文引用地址:http://www.eepw.com.cn/article/267760.htmFPGA既具有门阵列的高逻辑密度和高可靠性,又具有可编程逻辑器件的用户可编程特性,可以减少系统设计和维护的风险,降低产品成本,缩短设计周期。FIR数字滤波器在数字信号处理的过程中有很好的线性相位和稳定性,被广泛应用于音频处理、语音处理、信息系统等各种系统中。随着现代电子技术及EDA技术的发展,特别是可编程逻辑电路的发展,FIR数字滤波器的实现将变得更具有灵活性和实时性。

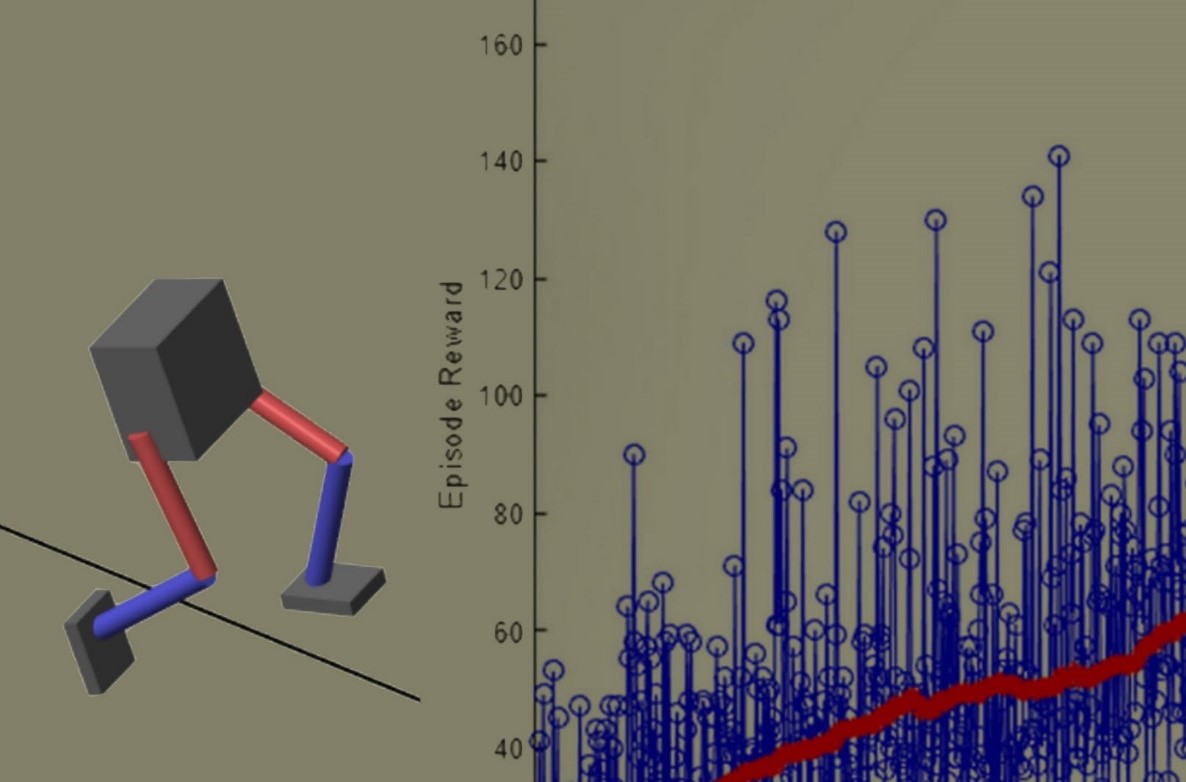

FIR 滤波器的设计与FPGA 高速实现一直是信号处理领域研究的热点,本文利用FIR 有限冲击响应滤波器IP 核,设计了截止频率为500Hz 的FIR 低通滤波器,在Simulink 中建立了仿真模型并进行了仿真。最终在EP2C35F672C8 型号FPGA 上得到了最高响应频率为151.88MHz 的高速FIR 低通滤波器。设计效率和滤波器性能得到了极大的提高。

利用Verilog HDL 设计数字滤波器的最大优点就是可使设计更加灵活。比较硬件电路图设计, Verilog HDL 语言设计的参数可以很容易在Verilog 程序中更改, 通过综合工具的简化和综合即可以得到电路图, 其效率要高出利用卡诺图进行人工设计许多。而且编译过程也非常简单高效。优秀编码风格能够在综合过程中节省芯片使用的单元, 从而降低设计成本。

本文只是利用Matlab辅助DSP实现了一个简单的FIR低通滤波器,并在TMS320C6713 DSK上成功运行。还可以利用Matlab辅助DSP来实现比较复杂的诸如语音处理、通信、图像处理等方面的程序开发,可以大大缩短DSP 应用程序的开发时间,提高设计效率,这也是以后DSP设计的一个趋势。

FIR滤波器具有幅度特性可随意设计、线性相位特性可严格精确保证等优点,因此在要求相位线性信道的现代电子系统,如图像处理、数据传输等波形传递系统中,具有很大吸引力。本文简单介绍了其线性相位条件和设计方法,并且提供了一种用DSP实现的方法。

本文主要探讨用频率采样法设计FIR数字滤波器的相关问题,主要包括设计原理、性能分析、线性相位条件及设计中应注意的问题等几个方面。

本文基于SoPC数字滤波器的设计与实现,不仅利用Matlab中的Simulink与Alterl DSP Builder工具确定FIR滤波器系数,不用编程,只需简单的设置,而且通过VHDL层次化设计方法,同时使FPGA与单片机相结合,采用C51及VHDL语言模块化设计思想进行优化编程。

滤波器相关文章:滤波器原理

fpga相关文章:fpga是什么

滤波器相关文章:滤波器原理

低通滤波器相关文章:低通滤波器原理

电源滤波器相关文章:电源滤波器原理

数字滤波器相关文章:数字滤波器原理

评论