基于FPGA 的FIR 数字滤波器设计方案

在QuartusⅡ环境下,数字滤波器的内部逻辑经过编译适配之后,以。sof文件的形式直接加载到FPGA中。

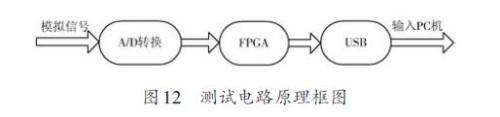

本文引用地址:http://www.eepw.com.cn/article/267746.htm进行实时测试的电路是应用FPGA和USB的数据采集电路,如图12所示。

测试时把信号发生器设置好的输入信号输入到A/D,采样得到的数据经过FPGA,再通过USB与PC机相连,应用QuartusⅡ中的SignalTapⅡ工具进行实时检测,结果如图13所示,其中,上面的波形为输入波形,频率为200 Hz,下面的波形为输出波形,由于200 Hz在低通的带通内,所以两者的波形相差不大。当输入波形为频率533 Hz时,由于是在截频点,其输出波形的幅值约为输入波形幅值的71%,如图13和14所示。

5结束

FIR数字滤波器在数字信号处理领域有着广泛的使用,本文通过仿真和实时验证两种方式实现了一种基于FPGA和DSP Builder的FIR数字滤波器。先根据FIR滤波器的基本原理和结构框图搭建了滤波器的模型,再根据滤波器的性能指标通过FDATool工具对其进行设计,并通过系统级仿真和ModelSim功能仿真进行了简要的可行性分析,最后通过QuartusⅡ软件对FIR数字滤波器进行实时验证,表明本方案所设计的FIR滤波器功能正确,性能良好。

滤波器相关文章:滤波器原理

fpga相关文章:fpga是什么

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

数字滤波器相关文章:数字滤波器原理

评论