零基础学FPGA(三)Verilog语法基基础基础(上)

—— 零基础学FPGA(三)Verilog语法基基础基础(上)

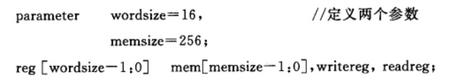

还有个地方我感觉不太明白,见下图,谁知道这句话上面意思...求大神解释...

本文引用地址:http://www.eepw.com.cn/article/267551.htm

下面这几句话需要注意

4、运算符及表达式

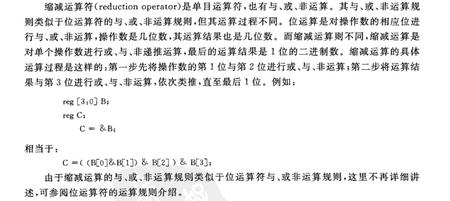

这里和C语言几乎一样,就不做过多解释了吧。就说一下位拼接运算符和位减运算符,这里C语言里面没有。

直接看个例子就可以

5、赋值语句

赋值语句共有两种,即非阻塞赋值,和阻塞赋值。

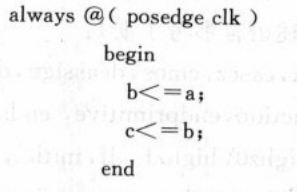

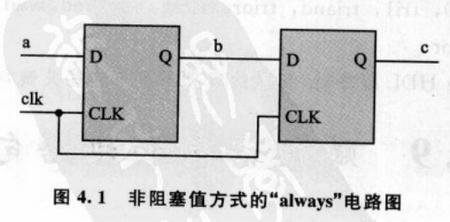

(1)非阻塞赋值

非阻塞赋值方式所赋值的变量不能立即就为下面语句所用,只有当块结束后才能得到上一次所附的值,这种赋值方式是编写可综合的时序逻辑时常用的赋值方式。例如

这个例子的意思是,当时钟上升沿到来时,a的值给b,b的值给c,但是只有当块结束时才完成赋值,这么说吧,假如原来a=1,b=2那么当时钟上升沿到来时a=1,b=2,c=2;当块结束时,a=b=c=1;

这么理解对吗?求大神指点...

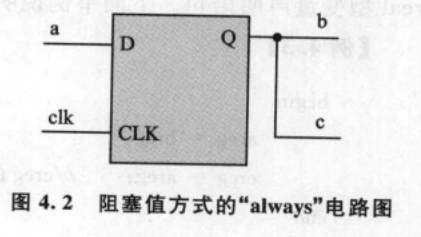

(2)阻塞赋值

与非阻塞赋值不同,赋值语句执行完后块才结束,b 的值在赋值语句结束后立刻改变,但是在时序逻辑电路中可能会出问题。

always @(clk or clr);

begin

b=a;

c=b;

end

假如开始a=1;当当时钟上升沿到来时,a=b=c=1;然后块结束

fpga相关文章:fpga是什么

c语言相关文章:c语言教程

评论