基于FPGA的数字日历设计

年月日模块计数设定为2000年~2999年,从图4中可以看出2008年2月,计数到29天;从图5得到2005年2月计数到28天;从图6看出2004年12月计数到31天,设计正确。

本文引用地址:http://www.eepw.com.cn/article/267018.htm3.4定时模块

定时模块通过按键K4来切换调节定时的分钟和小时,调整功能由调时模块的按键K3来完成,每按两下K3对应的显示加1.

3.5调时模块

调时模块设计思想是:通过把整个设计中的上一个模块(比如:分的上一个模块是秒;年的上一个模块是月,等等)的进位输出接到本模块的输入in,out接到下一个模块的时钟输入。正常状态下sout=fin,fout=hin,hout=din,dout=min,mout=yin,win=hout;当每按下两次K2键,产生一个上升沿分别对fin,hin,win,din,min,yin,dingshi调节,调节信号由K3给出。其中定义一个信号w,计数到7返0,对应正常状态,fin,hin,win,din,min,yin,dingshi 7个状态。

当K2每来一个上升沿时,分别对分,时,星期,天,月,年以及定时调整,调整信号由K3给出,经仿真调时模块结果与系统设计要求符合。

3.6控制模块

控制模块通过K1按键进行切换显示调整,起初显示年月日,按下2次K1显示时间,再按下2次显示定时时间。

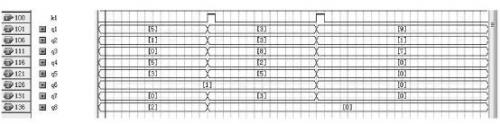

若仿真参数设置数值为:2013年05月15日,星期三,15:28(33 s),定时为07:19.仿真后结果如图7所示。

从图7可以看出,通过K1按键控制显示,开始显示年月日:20130515,当按下K1两下,显示星期+时间:03152833;再按两下显示定时时间:00000719.仿真结果与预期设计一致,设计正确。

图7仿真结果

3.7闹钟模块

闹钟模块设计为当定时时间到或者整点时闹铃响,分别有ZHENG,NAO两个控制端子控制,低电平有效。经验证,定时和整点报时仿真结果均符合设计要求。

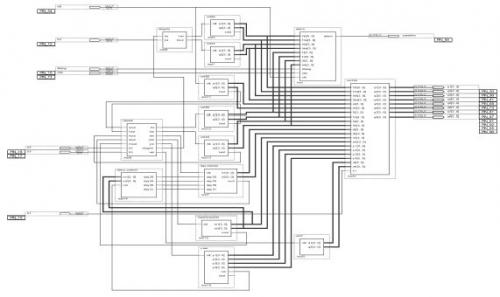

3.8顶层模块

将各个子模块设计好之后,并创建各自文件的图元,以供原理图设计文件中调用。然后在原理图编辑窗口创建顶层原理图文件shuzirili.bdf,即将各图元的引线端子按照逻辑关系连接起来,得到如图8所示的完整原理图,也即顶层模块。

对顶层文件分别进行时间、日期、闹铃功能的波形仿真,得到的仿真结果和预想设计一致,表明设计正确。

图8顶层原理图

伺服电机相关文章:伺服电机工作原理

分频器相关文章:分频器原理 尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论