TM1300 DSP系统以太网接口的设计

1 概述

本文引用地址:http://www.eepw.com.cn/article/266272.htm随着网络技术、多媒体技术的飞速发展,基于IP网络的多媒体应用越来越广泛。TM1300是Philips公司推出的一款高性能多媒体数字信号处理器芯片,适合于实时性强的音视频处理应用,可广泛应用于会议电视、可视电话、远程图像监控等应用场合。具有广阔的应用前景。

根据具体的基于IP网络上的多媒体应用系统的需要,采集的音视频数据经压缩处理后,一般要传送到远程终端或控制中心,这时就需要解决DSP应用系统与IP网络接口的问题。

考虑到国内局域网大部分是以太网,随着交换式网络、宽带网络的发展,使得基于以太网接入IP网络上的应用有着现实意义。

TM1300可以作为PC机的一个外设工作,此时可直接采用PC机上标准的以太网接口传输数据;TM1300支持独立引导,自成一个系统从而脱理PC环境工作,这为实际低价位高性能音频处理终端提供了可能。这种情况下,网络接口的设计就相对复杂一点,需要解决硬件接口电路的设计、基于实时操作系统pSOS+驱动程序的设计等。本文介绍以太网控制器CS8900A,并解决TM1300 DSP系统和CS8900A的硬件接口设计;简单介绍pSOS+操作系统内核中实现TCP/IP协议栈的网络模块pNA+,以及pSOS+操作系统下网络驱动程序的设计。

2 DSP芯片TM1300及X10总线接口

DSP芯片TM1300的核心是32位VLIW结构CPU,时钟频率可达166MHz,片内集成了SDRAM接口、PCI/XIO总线接口、图像协处理器、可变长解码器、音频输入输出接口、视频输入输出接口、同步串行通信接口等模块,各模块与SDRAM之间采用DMA方式传送数据。CPU各功能模块之间的协调、资源的分析、进程的调度,由运行在CPU上的一个由中断源触发的实时操作系统pSOS+控制。

网络控制器CS8900A是通过XIO总线与TM1300实现接口的。限于篇幅,这里重点介绍TM1300中用于外设端口扩展XIO总线。

TM1300片内的PCI/XIO复用总线接口给用户提供了无缝连接PCI设备及扩展8位外设端口的能力。当PCI/XIO总线接口中的XIO总线逻辑被激活时,作为TM1300系统扩展8位外设的总线,其中PCI-AD[23:0]为地址总线A23~A0,共提供了寻址16M个单元的能力;PCI-AD[31:24]为8位数据总线D7~D0;C/BE0#为读信号RD;C/BE1#为写信号WR;C/BE2#为数据选通信号DS。

3 CS8900A简介

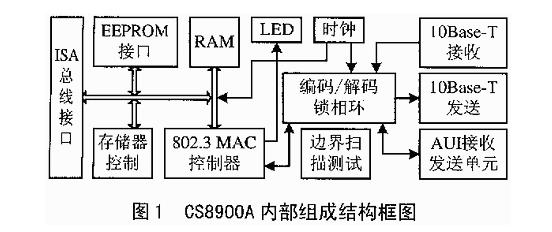

CS8900A是Cirrus公司生产的一种高集成度的全面支持IEEE802.3标准的以太网控制器,其组成结构框图如图1所示。CS8900A支持8位、16位的微处理器,可以工作在I/O方式或Memory方式。片内集成了ISA总线接口,可以直接和有ISA总线的微处理器系统无缝连接。片内集成了4KB容量的PacketPage结构的RAM,这4KB存储器映像结构的RAM包括片内各种控制、状态、命令寄存器,以及片内发送、接收缓存。用户可以以I/O方式、Memory方式或DMA方式访问它们。

之所以选择CS8900A,是因为Cirrus提供了CS8900A的基于各种操作系统的驱动程序源代码,这就为开发带来了方便。基于pSOS的驱动程序是假设目标系统中包含了Intel 80X86的CPU和1个16位的ISA总线接口的,而TM1300中用于扩展外设的XIO总线是8位总线,可见硬件设计的主要任务是实现8位XIO总线与16位ISA总线时序的配合。驱动程序的设计主要是解决基于80X86芯片的源代码移植到TM1300上运行的问题。

4 TM1300与CS8900A硬件接口电路设计

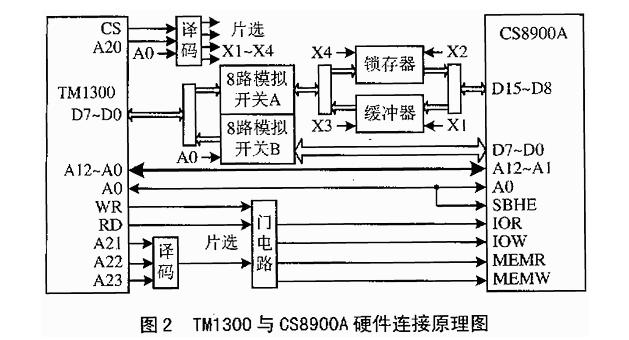

TM1300的XIO总线用于提供用户扩展外设,有8根数据线D7~D0,24根地址线A23~A0,还有I/O读写信号RD、WR。所以,利用TM1300的8位XIO总线模拟1个16位的ISA接口和CS8900A的ISA总线接口连接,即可解决硬件接口的问题。图2给出了接口设计的原理框图。

图2中,CS8900A的高8位数据线通过1个8位锁存器和缓冲器连接到8路模拟开关A的一端,CS8900A的低8位数据线连接到8路模拟开关B的一端。8路模拟开关A、B的另一端均连接到TM1300芯片XIO总线的数据线D7~D0上。8路模拟A、B在同一个时刻只有1组是连通的,由A0控制:A0=0时,模拟开关B连通;A0=1时,模拟开关A连通。这样就可以实现XIO总线8位数据线与CS8900A的16位总线的连接。同时,TM1300的A20、A0经译码控制锁存器和缓冲器的操作,逻辑关系如下:

①A20用于控制读写。当A20=0时,CS8900A的高8位数据从缓冲器输入;当A20=1时,高8位数据经锁存器输出到CS8900A的D15~D8。

②A0用于控制8位或16位操作。当A0=0时,对应16位数据读写;A0=1时,对应高8位数据读写。

对CS8900A的16位数据读和写操作有所不同。当TM1300从CS8900A读16位数据时,读16位数据(A0=0、A20=0),CS8900A的低8位数据直接通过8路模拟开关B输入到TM1300的XIO总线的8位数据线D7~D0;同时,高8位数据保存在缓冲器中,紧接着TM1300再读入缓冲器中的高8位数据(A0=1、A20=0)。同样,输出16位数据到CS8900A时,首先将要输出的高8位数据锁存到锁存器中(A0=1、A20=1),然后紧接着直接输出低8位数据到CS8900A的D7~D0(A0=0、A20=1),此时,锁存在锁存器中的高8位数据输出允许,也输出到CS8900A的D15~D8。

A12~A0直接连接TM1300的XIO总线的A12~A0。因此对于TM1300而言没有I/O和存储器的区别,所以WR经与片选取或后直接与CS8900A的IOW、MEMW连接。RD也是直接与CSCS8900A的IOR、MEMR连接。

tcp/ip相关文章:tcp/ip是什么

评论