基站对高集成度低噪声放大器的要求

由于调整器和低噪放晶体管使用相同的制程被集成在一起,因此Vbias和VGS可以相互作用。这种作用一方面通过校准温度的偏移来帮助确保Ids的温度稳定度,另一方面有助于补偿在晶圆工作时的跨导变化。这些技术已全部应用在MGA-63X系列LNA。

本文引用地址:http://www.eepw.com.cn/article/266248.htm偏压调整器可以通过改变外部的电压(Vbias)来调整低噪放的静态电流(Ids)。其驱动电流(Ibais<1mA)和大多数的CMOS器件相当。可以直接连接到系统的控制器引脚,然后控制低噪放的开关状态使其应用在时分模式。

可 调节的偏压特性使得工程师在使用器件时需要在功耗和线性度上做取舍。在不需要高线性度的应用中,工程师可以通过增加Rbias(正常为6.8k欧姆)的电 阻来达到省电的目的。或者在增益和输出功率变化不大(ΔG和ΔP1dB≤0.5dB)的情况下,通过改变Idd的电流(25~75mA),使得低噪放的 OIP3产生大约10dB的变化。这使得具有微控制器控制Vbias的低噪放对频谱拥挤的自适应能力大大增强。

无论是晶体管的设计 还是偏压调整器的工作,都在尽量避免使用额外的匹配网络。主要是担心会带来插入损耗和噪声系数的增加。晶体管的几何结构和它的标准电流已经可以保证其输入 阻抗在50欧姆附近。内部集成的动态偏压调整器通过外加电阻的方式也可以保证其不影响低噪放的输入阻抗。这些措施都是用来保证低噪放不需要外加的输入匹 配,帮助获得最小的噪声系数。

评估板的性能

为评估MGA-63X系列低噪放的特性,安华高制作了MGA-633P8的demo板,并在最少外围器件的情况下,测试了其900MHz的特性。外围器件的值是通过简单的仿真获得,没有进行最优化仿真设计。更多的EVB的仿真信息请参考安华高的应用文档AN-5457。

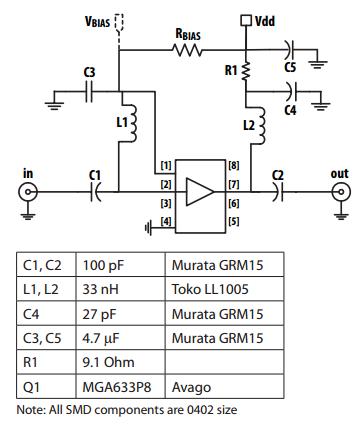

MGA-633P8的DEMO板原理图如下:

在上图中,输入电感L1仅具有射频信号抑制器的功能,低噪放的输入损耗对输入谐振器的空载Q值并不是特别灵敏。仿真显示,输入谐振器空载Q值在20到100 的范围内变化,噪声系数的变化量小于0.05。这表明,无论是使用0402的多层贴片电感还是使用空心的绕线电感,对低噪放的都影响很小。对输入谐振器的 低要求主要用来确保低噪放设计的低成本和小尺寸。

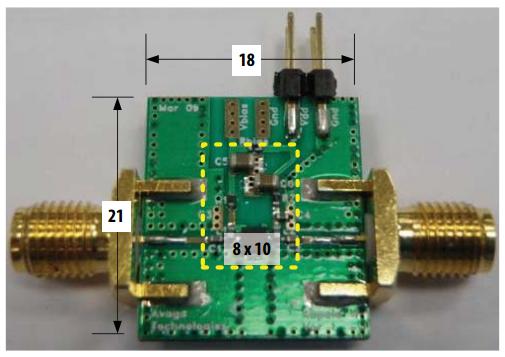

EVB的制作图例如下:

图 中PCB的尺寸为21.5×18×1.4mm,PCB板材有两层,顶层为Rogers的RO4350,厚度为10mil,底层为低成本的FR4,厚度为 1.2mm,二者的接地铜箔紧紧的结合在一起。射频连接器是Johnson的SMA接头,DC电源接头是2-pin的连接器,被动元件的尺寸都是0402 的,这样整个元器件区域的大小约为8×10mm2。

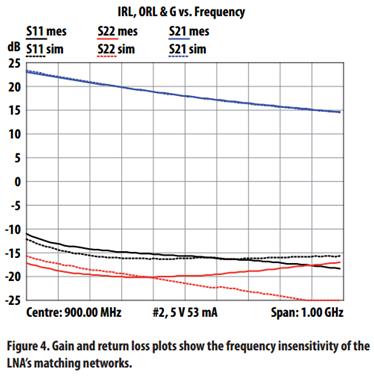

EVB的测试结果如下图:

电子管相关文章:电子管原理

双工器相关文章:双工器原理

评论