基于CPLD的DSP多SPI端口通信设计

引言

本文引用地址:http://www.eepw.com.cn/article/257461.htm目前在电气自动化控制装置中,广泛采用各种通信手段以完成上层与底层控制器、底层控制器以及控制芯片之间的信息传递,并实现相应的控制功能;各种通信功能的设计与实现已成为自动化装置设计的重要组成部分。本文以一种超声波电机运动控制装置为应用背景,讨论了基于CPLD的DSP控制芯片多SPI端口通信技术。

串行同步外设端口(SPI)通常也称为同步外设端口,具有信号线少、协议简单、传输速度快的特点,大量用在微控制器与外围芯片的通信中。目前SPI通信方式已被普遍接受,带有SPI端口的芯片越来越多,如Flash、RAM、A/D转换、LED显示、控制专用 DSP芯片等。

本文介绍一种采用运动控制专用DSP芯片DSP56F801设计的超声波电机运动控制装置。由于该超声波电机需要采用两相四路对称.PWM信号来实现驱动控制,而DSP芯片无法直接产生所需PWM信号,采用软件方法又会占用大量的DSP计算时间,于是设计了基于可编程逻辑器件(CPLD)的对称PWM信号发生器。该信号发生器在DSP的控制下,可以实现输出两相PWM控制信号的占空比及相位差调节;同时采用具有SPI接口的可编程振荡器LTC6903,实现在DSF。控制下的PWM控制信号频率调节[1]。由此可见,为了实现DsP对PwM控制信号占空比、相位差及频率的控制,需要采用适当的通信方式实现DSP与CPLD及LTC6903之间的控制信息传递。DSP56F801芯片具有一个SPI通信端口。本文在分析SPI 数据传输时序关系的基础上,设计并实现了基于CPLD的多SPI接口通信。

1 工作原理

SPI是一个同步协议接口,所有的传输都参照一个共同的时钟。在同一个SPI端口可以实现一个主机芯片与多个从机芯片的相连,这时主机通过触发从设备的片选输入引脚来选择从设备,没有被选中的从设备将不参与SPI传输。SPI主使用4个信号:主机输出/从机输人(MOSI)、主机输入/从机输出(MISO)、串行时钟信号SCLK和外设芯片选择信号(SS)。主机和外设都包含一个串行移位寄存器,主机通过向它的SPI串行移位寄存器写入一个字节来发起一次传输。寄存器是通过MOSI引脚将字节传送给从设备,从设备也将自己移位寄存器中的内容通过MISO信号线返回给主机。这样,两个移位寄存器中的内容就被交换了。外设的写操作和读操作是同步完成的,因此SPI成为一个很有效的串行通信协议[2]。

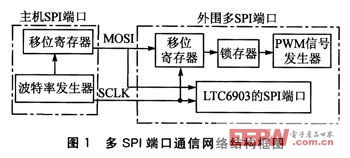

SPI端口的通信网络结构框图如图1所示。为了使信号发生器输出可调频、调压和调相输出的两相四路PWM波,需要DSP向CPLD电路输出参数。这4个控制参数的传递是在小型的通信网络中实现的。在该网络中,DSP的SPl只是进行数据输出端口的写操作,即输出电压控制字、相位控制字和频率控制字。数据流程:主机DSP向cPLD传输数据,在传输数据时,数据在MOSI引脚上输出,同时数据在时钟信号的作用下实现同步移位输出。由于不需要从机向主机回送任何数据,主机在数据传输结束之后,结束这次传送。由于sPI端口工作时没有应答信号,并且数据在发送时无需校验位,所以要求主、从器件的数据发送与接收必须完全符合设定的SPI时序要求,否则数据传输将出现错误。

2 基于CPLD的串口SPI设计

2.1移位寄存器设计

本设计为一个12位的SPI串行接收端口。图1中移位寄存器是由12个D触发器和1个计数器组成的,实现移位接收和串并转换。在传输过程中,先使能移位寄存器和计数器,启动传输,同时计数器开始计数。当计数到16时,进位端输出一个脉冲宽度的高电平脉冲,进行数据锁存,其电路如图2所示。

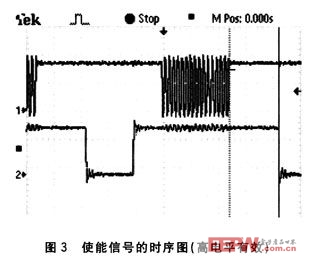

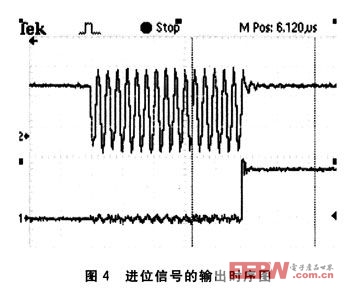

实验中为保证时序正确,测出了使能信号和计数器进位脉冲的输出时序,如图3、图4 所示。其中十六进制计数器采用的是上升沿计数,在第16个上升沿到来时,跳变为高电平,保证数据的正确接收锁存。

2.2锁存器设计

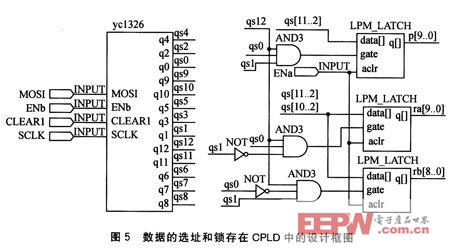

锁存器的工作特点:当gate引脚上输入高电平信号时,锁存器工作开始锁存总线上的数据;当gate引脚上是低电平时,锁存器不工作,即当总线上的数据发生变化时,锁存器的输出不发生变化。由于本设计需要多个参数传输,通过地址选择的方法把这3个数据从一条总线上区分出来,设置传输数据的低两位为地址选择位。地址选择位经移位寄存器,串并转换,作为三输入与门的两个输人端,进行地址选择。每次16位的数据移位结束,数据稳定时,在计数器高电平作用下,相应gate的引脚上输出高电平,数据锁存入相应的锁存器。例如,可以设置低两位是“ll”时,DSP送入PWM电路的是ll位的调相信号;当低两位设置成“01”时,DSP送入PwM电路的是10位调节A 相占空比的信号;当低两位设置成“10”时,。DSP送入PWM电路的是10位调节B相占空比的信号。由此可以在电路中设计一个三输入的与门,当16位数据传输完毕,即在相应gate的引脚上输出高电平时,数据存入对应的锁存器,如图5所示。

评论